低消費電力の組み込みビジョンを車載/医療機器に:ラティスがソリューションを追加(2/2 ページ)

384ビット暗号化に対応「Lattice Sentry 2.0」

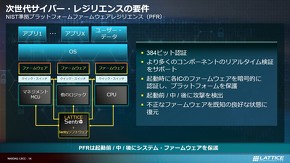

Lattice Sentry 2.0は、ラティスのセキュア制御FPGA「Mach-NX」に対応する。「NIST PFR(プラットフォームファームウェアレジリエンス)ガイドライン」に準拠し、384ビット暗号化をサポートする次世代ハードウェアRoot-of-Trust(HRoT)ソリューションを実現する。

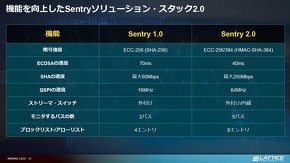

Lattice Sentry 2.0で強化した機能は主に3つある。まずは384ビット暗号化の対応だ。「今後のサーバプラットフォームには、384ビット暗号化が必須だとされている」とラティスは説明する。2つ目は、起動前認証を従来比で4倍に高速化したことだ。「Lattice Sentry 2.0では、ECDSA(楕円曲線DSA)の速度は70ミリ秒、SHA(Secure Hash Algorithm)の速度は最大60Mビット/秒、QSPIの速度は16MHzを実現している。こうした機能によって、起動時間を大幅に短縮し、システムのダウンタイムを最小に抑えられる。起動プロセス中のファームウェアへの攻撃に対するリスクも低減できる」(同社)

3つ目の強化ポイントは、最大5つのファームウェアをリアルタイムでモニタリングする機能だ。システムの起動時および動作中に、メインボードコンポーネントを5つまで、リアルタイムでモニタリングする。「競合するMCUベースのセキュリティソリューションは、このようなモニタリング機能は備えていないことが多い」とラティスは説明する。

なお、「Lattice Sentry 2.0の性能向上は、Mach-NXのアクセラレーターによるもの。そのため、セキュア制御FPGAの従来品である「MachXO3D」では、Lattice Sentry 1.0の性能しか出せないことになる」(ラティス)

関連記事

ラティス、28nmFD-SOIの新FPGAプラットフォーム

ラティス、28nmFD-SOIの新FPGAプラットフォーム

Lattice Semiconductor(ラティスセミコンダクター)は2019年12月10日(米国時間)、28nm FD-SOI(完全空乏型シリコン・オン ・インシュレーター)を採用した新たな低消費電力FPGAプラットフォーム「Nexus」および、その最初の製品となる「CrossLink-NX」を発表した。 384ビット暗号対応のFPGA、「PFR」の実装が容易に

384ビット暗号対応のFPGA、「PFR」の実装が容易に

Lattice Semiconductorの日本法人であるラティスセミコンダクター(以下、ラティス)は2020年12月10日、サイバーレジリエンス向けに、セキュリティ機能を強化したFPGA「Mach-NX」を発表した。2019年に発表した「MachXO3D」の機能をベースとしたもので、MachXO3Dに続く第2世代品となる。 電池駆動も可能な超低消費電力AI、Latticeが展示

電池駆動も可能な超低消費電力AI、Latticeが展示

2019年10月15〜18日にかけて、「CEATEC 2019」が千葉・幕張メッセで開催される。Lattice Semiconductor(ラティスセミコンダクター)は、同社の最新FPGAやソリューションを展示する。 超小型FPGAをエッジに、独自路線を進むLattice

超小型FPGAをエッジに、独自路線を進むLattice

小型で低消費電力のFPGAを手掛けるLattice Semiconductorは、クラウド市場に注力する他のFPGAベンダーとは明確に路線を分け、エッジ向けに力を入れる。 投資ファンドによるLattice買収が破談に

投資ファンドによるLattice買収が破談に

未公開株式投資ファンドCanyon Bridge Capital Partnersによる米Lattice Semiconductorの買収は、トランプ大統領が発令した大統領令を受けて破談になった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増