光トランシーバーのForm Factorの新動向(6) 〜電気と光のインタフェース:光伝送技術を知る(17) 光トランシーバー徹底解説(11)(4/4 ページ)

3.2T CPO要求仕様

Co-packaged-Optics CollaborationがWorking Groupで検討してきたCPOの仕様を発表した(ドキュメントはこちら)。タイトルは”3.2 Tb/s Co-packaged Optics Optical Module Product Requirements Document”。このドキュメントは、OIFに2020年12月に作られたCo-packaged Optics Frameworkのもとで仕様化される予定で議論が始まっている。

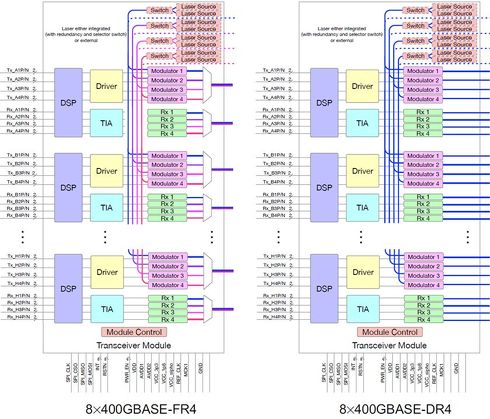

Scopeにあるように3.2T CPOで51.2Tスイッチを可能とするBuilding Blockとし、400GBASE-FR4と400GBASE-DR4の光インタフェースを用いた2種類のモジュールを定義している。未確定(TBD)が多いが、ポイントを紹介する。

(1)構成

ガイドラインでは6.4Tのデータ容量とされていたが今回は3.2Tとなっている。OIFの議論では2×1.6Tである。光インタフェース仕様は400GBASE-FR4と400GBASE-DR4となっている。モジュールとしては8x400GBASEであり、400GBASE-FR4ではファイバー送受8本ずつ16本、400GBASE-DR4ではファイバー送受32本ずつ64本である。もちろん、この64本が最大のチャレンジの一つである。

また、OIF-CEIでも200Gbit/s電気インタフェース、IEEE802.3の800GbEでは200Gbit/s per Lambda光インタフェース議論も始まっており、実用時期を含め今後の議論に注目だ。集積チャネル数やモジュール幅などからSi-photonicsありきで進んでいると思われるが、Si-photonicsでも200Gbit/sも可能という方向でIEEEでの議論も行われているので無視はできないと考える。

これを含め、購入仕様書のような今回のドキュメントには違和感があるが、OIFでもまれて良い方向に行くことを願っている。

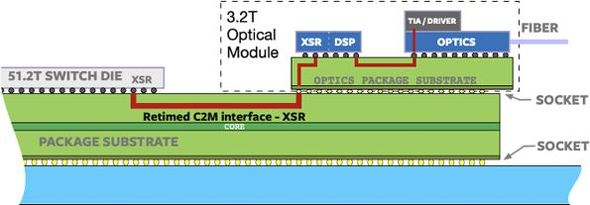

以下のような断面図も示してある。TIA/DRIVERがピギーバックになっており、DSPのアナログ信号はPhotonics substrateを駆け上りTIA/DRIVERに接続される。

(2)環境・消費電力

面白い仕様である。消費電力が大きいIn-Box Light Sourceの場合は内部にレーザーがあるため最高ケース温度が低く、消費電力が小さいExternal Light Sourceの場合は最高ケース温度が高い。モジュールサイドからみると当然のように思われるが、エンドユーザーから考えると冷却系か外部光源部品かの選択となっているのだ。もちろんIn-BoxかExternalかは信頼性やファイバーなど他の要素で総合的に判断される。

Energy Efficiency(EE)はそれぞれ15pJ/Gbitと17.5pJ/Gbitと、400Gでは6Wと7Wであり、低く設定されているとはいえず、1〜2年の実現可能性を考慮したものと思われる。

(3)光インタフェース

光インタフェース仕様は400GBASE-FR4と400GBASE-DR4に加えて、200GBASE-FR4も可能にすることとしている。

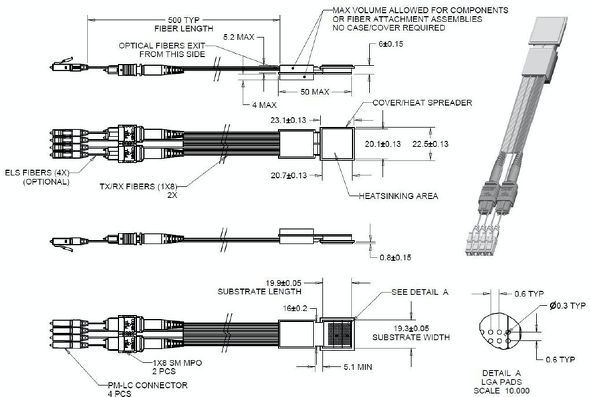

光の実装インタフェースは8芯MPOで、16芯MPOも可能としている。

外部光源の場合は偏波保存ファイバー(Polarization Maintenance Fiber、PMF)を用いたLCコネクターとなっている。外部光源用ファイバーは4本。なお、直前の図で「MPOコネクター」になっているのは誤記と思われる。

(4)電気インタフェース

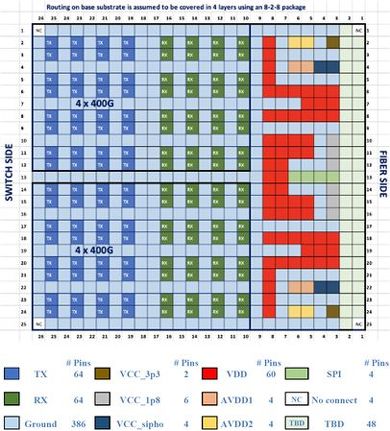

電気インタフェースはOIF-CEI-XSRである。電気入力実装インタフェースはLGAソケットで0.6mmピッチである。

ピンマップも示されている。電源にVender specificなVcc-siphoという、シリコンフォトニクス用に必要だと思われるVendor Specific電源があるのに注意が必要だ。

(5)外形

外形も示されている。ただし、400GBASE-FR4の場合でファイバー本数の多い400GBASE-DR4の仕様は今後に残されている。

OE部の幅は22.5mmである。OE部の長さは23.1mmであり、隙間なく並べたときのMCMの長さは136.2mm(22.5x4+22.5x2)となる。150mmのMCMとすれば10%程度の隙間マージンとなる。なお、CPOパッケージ基板は19.3mm×19.9mmとなっている。

ファイバー接続部の長さは30mmであり、レセプタクルやショートピッグテールの場合もこの長さに以下に抑える必要がある。ファイバー長は500mmと19インチBoxとほぼ同じだ。私の経験では短すぎると考える。同じ長さでファイバールーティングするには最低でもMCMの周りを1周してFront Panelに接続する長さが必要だと考える。

ヒートシンクは上部にThermal Interface Material(TIM)を介して取り付けられ冷却する。そのサイズは20.1mm×20.7mmである。

底面図にあるOE部とファイバー接続部の間に5.1mmの隙間が指定されているのはLGAソケットを含むCPO固定のフィクスチャーが想定されていることを想像させる。

(6)信頼性

信頼性に関しては以下のように記述されており、これからの議論である。レーザーをIn-packageにする場合、下記を達成できるかどうかが大きな分かれ目になる可能性がある。また、FIT数によってクラス分けすることも議論されている。

「The CPO FIT rates will be specified to guarantee an AFR of <1% for the 51T CPO-based switch. This will require some adjustment to the FIT levels at the 3.2T optical level.」

以上、CPO Collaborationから発行された3.2T CPOの要求仕様を紹介した。このDocumentを基に、OIFで標準化を進める予定である。

仕様としてはまだまだほとんどの項目が決まっていない。これからのオープンな議論が期待される。

1. 最大の問題は400GBASE-DR4方式の仕様、特に外形仕様が決まっていないことでこの仕様を優先的に決めるか、落としてしまうかの選択に迫られるだろう。

2. 200Gbit/s電気と光インタフェースが実用化時期には必要になると思われる

3. Si-photonicsだけではなくアレイ化に向いていて低価格のVCSEL/MMFの仕様化も必要と考える

4. CPOに関連した未熟な技術の開発を急ぎ、仕様に反映させる必要がある

4はPackage-on-package(PoP)実装、Fiber Attach、Laser Attach、Detachable Optical Connector(必要と考える)、Low cost & profile & high speed compact LGA connector(<0.4mmピッチ)などである。

筆者プロフィール

高井 厚志(たかい あつし)

30年以上にわたり、さまざまな光伝送デバイス・モジュールの研究開発などに携わる。光通信分野において、研究、設計、開発、製造、マーケティング、事業戦略に従事した他、事業部長やCTO(最高技術責任者)にも就任。多くの経験とスキルを積み重ねてきた。

日立製作所から米Opnext(オプネクスト)に異動。さらに、Opnextと米Oclaro(オクラロ)の買収合併により、Oclaroに移る。Opnext/Oclaro時代はシリコンバレーに駐在し、エキサイティングな毎日を楽しんだ。

さらに、その時々の日米欧中の先端企業と協働および共創で、新製品の開発や新市場の開拓を行ってきた。関連分野のさまざまな学会や標準化にも幅広く貢献。現在はコンサルタントとして活動中である。

関連記事

光トランシーバーのForm Factorの新動向(3) 〜FacebookやMicrosoftが主導するCPO

光トランシーバーのForm Factorの新動向(3) 〜FacebookやMicrosoftが主導するCPO

2000年以降データセンターを支えてきたSFP、QSFPなどのFront Panel Pluggable光トランシーバーから根本的に変革し、次世代の主流になるかもしれないCPOを解説する。 「光トランシーバー」は光伝送技術の凝縮

「光トランシーバー」は光伝送技術の凝縮

今回から、光トランシーバーについて解説する。データセンター、コンピュータや工場内ネットワークで使用される80km程度以下の中短距離光リンクを中心に、ストレージ、ワイヤレスやアクセス通信ネットワークなど、多様なアプリケーションで使用されている光トランシーバーを紹介する。 光ファイバーとシリコン光導波路を結合する技術

光ファイバーとシリコン光導波路を結合する技術

今回は、光ファイバーとシリコン光導波路を結合する技術を解説する。 100Gbpsを超える光ファイバー高速伝送へのアプローチ

100Gbpsを超える光ファイバー高速伝送へのアプローチ

今回は、100Gビット/秒(bps)と極めて高速な変調信号を光ファイバーで伝送する実験結果を紹介する。 「802.11ah(Wi-Fi HaLow)」の実証実験を公開

「802.11ah(Wi-Fi HaLow)」の実証実験を公開

802.11ah推進協議会は、IoT(モノのインターネット)通信システムに向けたWi-Fi規格「IEEE 802.11ah(Wi-Fi HaLow)」について、総務省から「実験試験局免許」を取得した。「ワイヤレスジャパン2019」でその実証実験を公開する。 データセンターを支える光伝送技術 〜ハイパースケールデータセンター編

データセンターを支える光伝送技術 〜ハイパースケールデータセンター編

今回は、エンタープライズデータセンターに続き、GoogleやFacebook、Appleなどが抱える巨大なデータセンター、「ハイパースケールデータセンター」について解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増