シリコンフォトニクスへのアプローチ:福田昭のデバイス通信(343) TSMCが開発してきた最先端パッケージング技術(16)

今回から、「シリコンフォトニクス」に関する講演部分を紹介していく。

あまり公表されていなかったTSMCのシリコンフォトニクス研究

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」が昨年(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。今回から、最後のテーマである「Si Photonics Integration(COUPE)」の講演部分を紹介する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。今回から、最後のテーマである「Si Photonics Integration(COUPE)」の講演部分を紹介する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)本シリーズの第13回から前回までは、シリコンダイを積層するモジュール「SoIC(System on Integrated Chips)」を想定した高性能放熱技術に関する講演部分を説明してきた。

今回から、最後のパートである「シリコンフォトニクス」に関する講演部分を紹介していく。TSMCはこれまで、シリコンフォトニクスに関する研究開発をあまり公表してこなかった。imecやIntelなどが積極的に研究成果を公表してきたのと比べると、積極さに欠けている、あるいは後発企業であるように感じられる。

一方でTSMCが学会で発表してきた半導体の研究成果には遊びが少なく、発表テーマの大半を事業化してきたという印象がある。研究開発機関であるimec、事業化時期が未定の研究にも予算を付けてきたIntelとは対照的なスタンスだ。TSMCが学会で発表してきた研究成果は「顧客が付く予定」のテーマだとも言える。研究色の強かった「シリコンフォトニクス」をTSMCが手掛けるということは、近い将来には事業化する可能性が高い、と推測される。

データセンターの性能向上がシリコンフォトニクスの導入を迫る

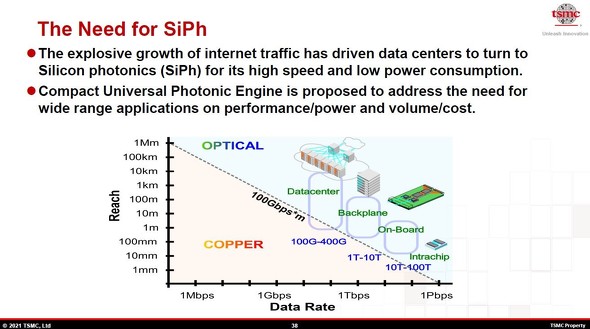

インターネットのトラフィックが急速に増加していることが、データセンターにおけるシリコンフォトニクスの重要さを高めている。速度の向上と消費電力の抑制を両立させるためだ。この分野では小型かつ汎用のフォトニクスエンジン(光電子集積回路)を必要とするという。

シリコンフォトニクス(SiPh:Silicon Photonics)の必要性[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

シリコンフォトニクス(SiPh:Silicon Photonics)の必要性[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)データ転送における銅ケーブル(銅配線)と光ファイバの境界は、100Gbps×mにあるとされる。転送速度と転送距離の積で決まる。境界を超えると、光ファイバ伝送が合理的な転送手段となる。データセンターでのシステム間伝送、バックプレーン間伝送、オンボード伝送、パッケージ内チップ間伝送などが、急速に光ファイバ伝送、あるいは光伝送の領域に入りつつある。

シリコンフォトニクスの実装手段

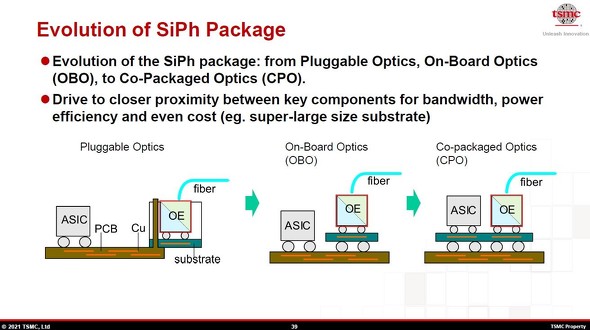

半導体ロジックのASICが入出力する高速信号を、光電変換回路(OE)を介して光ファイバでやりとりする回路の実装形態を説明しよう。かつてはプリント基板に搭載したASICを、プリント基板にプラグ接続した光電変換回路と接続していた。次に光電変換回路をサブ基板に搭載し、プリント基板にサブ基板を載せることでASICと接続するようになった(オンボード接続)。さらに、サブ基板にASICと光電変換回路の両方を搭載して両者の距離を縮めている(コパッケージ接続)。

ASICと光電変換回路(OE)の距離を短くすることは、データ伝送帯域と電力効率の向上に欠かせない。さらには製造コストを下げることにもつながる。

ASICと光電変換回路(OE)の実装手段の変遷。左のプラグ接続から中央のオンボードオプティクス(OBO)、右のコパッケージオプティクス(CPO)へと変化してきた[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

ASICと光電変換回路(OE)の実装手段の変遷。左のプラグ接続から中央のオンボードオプティクス(OBO)、右のコパッケージオプティクス(CPO)へと変化してきた[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 シリコンフォトニクスの技術開発ロードマップ

シリコンフォトニクスの技術開発ロードマップ

今回は、シリコンフォトニクスの技術開発ロードマップを解説する。シリコンフォトニクスの性能向上とコストを、16/14nmから5nm、3nmの技術ノードに沿って見ていこう。 光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に

今回は、“Beyond 400G”に向けた議論とともに、Pluggableにおける3つの問題点を紹介する。 シリコンフォトニクスデバイスの試作体制を構築

シリコンフォトニクスデバイスの試作体制を構築

産業技術総合研究所(産総研)電子光技術研究部門とTIA推進センターは、シリコンフォトニクスデバイスの試作体制を構築した。国内外の民間企業や大学もこれらの設計製造環境を利用することができる。 NEDOら、オンボード光モジュールで400Gbps実現

NEDOら、オンボード光モジュールで400Gbps実現

新エネルギー・産業技術総合開発機構(NEDO)と光電子融合基盤技術研究所(PETRA)は、外形寸法が34×36×8mmと極めて小さいオンボード光モジュールを用いて、400Gビット/秒(bps)の伝送速度を実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング