シリコンダイを直接水冷する次世代放熱技術の実力:福田昭のデバイス通信(342) TSMCが開発してきた最先端パッケージング技術(15)

今回は、3種類の放熱構造で冷却性能を比較した結果を紹介する。

シリコンダイの表面積拡大が冷却性能を強化

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」が昨年(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。前々回から3番目のパート「New Heterogeneous Integrations」の講演部分を説明している[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン。前々回から3番目のパート「New Heterogeneous Integrations」の講演部分を説明している[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)前々回から、異種のデバイスを集積化する技術に関する講演(「New Heterogeneous Integrations」)部分の紹介を始めた。講演で説明した技術は2つある。最初が放熱(冷却)技術、次がシリコンフォトニクス技術となる。前回では、3次元積層モジュール「SoIC」に向けた高性能冷却技術「ISMC(Integrated Si Micro-Cooler)」の概要と、放熱用シリコンダイの表面加工が冷却性能を大きく左右することを述べた。具体的には、シリコンダイの表面に角柱のアレイを形成し、その間に冷却水を通すことで放熱性能を大幅に高められることを確認した。

今回は、回路用シリコンダイ(実際には回路を形成したと仮定したシリコンダイ)と放熱用シリコンダイを積層する構成(放熱構造)の違いにより、熱抵抗がどのくらい変化するかを測定した結果を説明しよう。

3種類の異なる放熱構造で冷却性能を比較

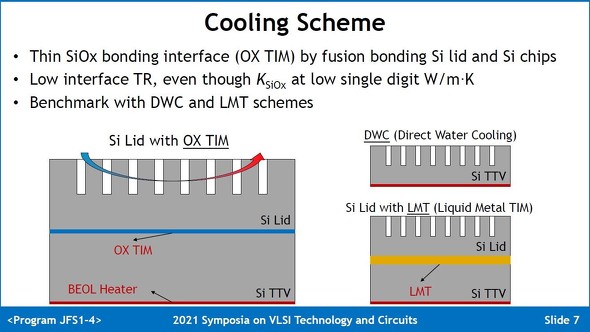

実験では、おおよそ3種類の放熱構造を用意した。(1)回路を形成した(と仮定した)シリコンダイ(TTV:Thermal Test Vehicle)と、放熱用シリコンダイ(Si Lid)を液体金属(LM:Liquid Metal)のTIM(Thermal Interface Material)を介して接続した構造(略称:LMT)、(2)回路を形成したシリコンダイ(TTV)と放熱用シリコンダイ(Si Lid)を、シリコン酸化膜(OX)のTIMを介して接続した構造(略称:OX TIM)、(3)回路を形成したシリコンダイ(TTV)の表面に角柱アレイを形成した構造(略称:DWC(Direct Wafer Cooling))、である。いずれの構造も、回路動作による発熱を模擬するヒーター(BEOL Heater)をTTVの表面に作り込んだ。

実験に使用した3種類の放熱構造。左は、回路を形成した(と仮定した)シリコンダイ(TTV:Thermal Test Vehicle)と放熱用シリコンダイ(Si Lid)をシリコン酸化膜(OX)のTIM(Thermal Interface Material)を介して接続した構造(略称:OX TIM)、右上は回路を形成したシリコンダイ(TTV)の表面に放熱用の角柱アレイを形成した構造(略称:DWC(Direct Wafer Cooling))、右下は回路を形成したシリコンダイ(TTV)と放熱用シリコンダイ(Si Lid)を液体金属のTIMを介して接続した構造(略称:LMT)。いずれも底面にヒーターを作り込んでいる[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)

実験に使用した3種類の放熱構造。左は、回路を形成した(と仮定した)シリコンダイ(TTV:Thermal Test Vehicle)と放熱用シリコンダイ(Si Lid)をシリコン酸化膜(OX)のTIM(Thermal Interface Material)を介して接続した構造(略称:OX TIM)、右上は回路を形成したシリコンダイ(TTV)の表面に放熱用の角柱アレイを形成した構造(略称:DWC(Direct Wafer Cooling))、右下は回路を形成したシリコンダイ(TTV)と放熱用シリコンダイ(Si Lid)を液体金属のTIMを介して接続した構造(略称:LMT)。いずれも底面にヒーターを作り込んでいる[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから) 回路用シリコンダイ(実際には回路を形成したと仮定したシリコンダイ)「TTV:Thermal Test Vehicle」の概要。配線工程を利用して銅(Cu)のヒーターとCuベースの測温抵抗体(RTD:Resistance Temperature Detector)を作製した。シリコンダイ面積は780mm2、ヒーター部分の面積は540mm2とかなり大きい[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)

回路用シリコンダイ(実際には回路を形成したと仮定したシリコンダイ)「TTV:Thermal Test Vehicle」の概要。配線工程を利用して銅(Cu)のヒーターとCuベースの測温抵抗体(RTD:Resistance Temperature Detector)を作製した。シリコンダイ面積は780mm2、ヒーター部分の面積は540mm2とかなり大きい[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)500mm2を超える大面積の高性能チップでキロワットを許容

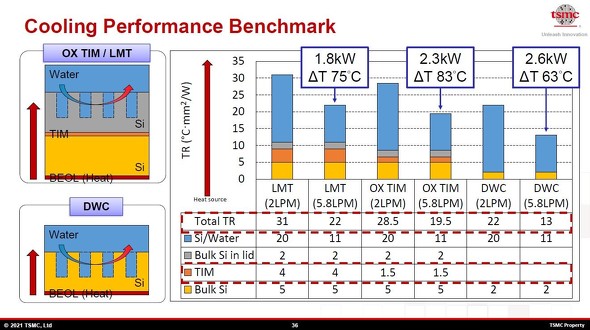

これら3種類の放熱構造を治具に組み込んで、冷却水の流量を変えて熱抵抗(ここでは熱伝達係数の逆数)を測定した。冷却水の流量は2リットル/分と5.8リットル/分、冷却水の温度は25℃である。

同じ流量で比較すると、熱抵抗の高い順から、(1)の構造(LMT)、(2)の構造(OX TIM)、(3)の構造(DWC)となった。現時点で実用的な構造は「LMT」と「OX TIM」であり、「OX TIM」の熱抵抗が低い。シリコンダイ面積が500mm2を超える大規模な高性能チップに「OX TIM」の放熱構造を追加することで、キロワット(kW)級の消費電力を許容できるようになるとする。

3種類の放熱構造で熱抵抗を測定した結果[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

3種類の放熱構造で熱抵抗を測定した結果[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)なお、最も熱抵抗の低い「DWC」は、回路を形成したシリコンウエハーの裏面を機械加工(ダイシングソーによる加工)することになる。回路の動作速度や信頼性などへの影響を精査する必要がある。このためDWCは、さらに将来に向けた技術と位置付ける。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待