EE Times Japan >

製品解剖 >

群雄割拠のチップレット 「理にかなった」戦略をとっているのは?:この10年で起こったこと、次の10年で起こること(88)(4/4 ページ)

» 2025年01月14日 11時30分 公開

[清水洋治(テカナリエ),EE Times Japan]

大手のスーパーハイエンドチップ

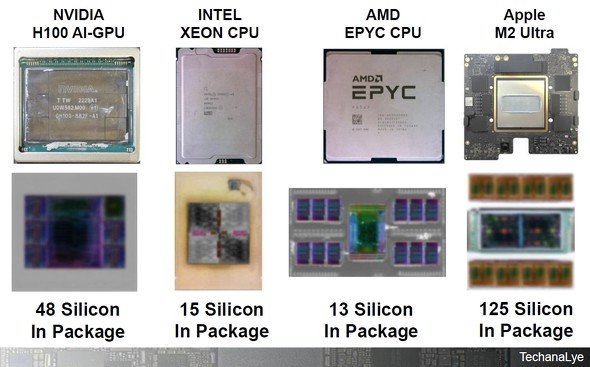

図6は2022年以降の大手半導体メーカーのスーパーハイエンドチップの様子である。各社各様の作り込みだが、1パッケージに多くのシリコンが収納されている。CoWoS(Chip on Wafer on Substrate/フル活用もあれば部分適応もある)なども活用されるが、各社異なる取り組みを行っている。学会や企業広告で発表されない技術も実際には多数活用されている(分解すればすぐに分かる)

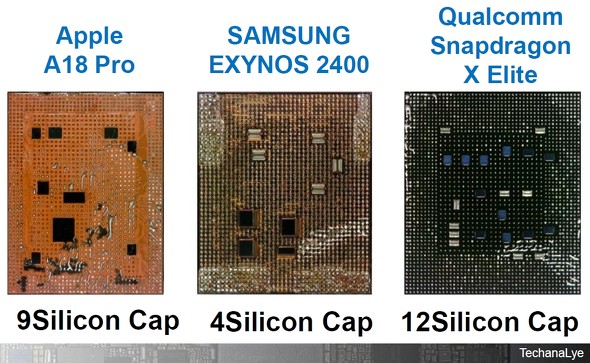

図7は2024年に発売されたスマートフォン/PC向けのInFO(Integrated Fan-Out)技術が採用されたプロセッサの端子とシリコンキャパシターの数である。今後はパッケージ内で機能と特性の両者を作り込むことが主流になっていく。

2025年も、“モノ”(実物)を見て判断していきたい(長年の半導体メーカー内での設計開発やマーケット企画で、モノを見ないで判断ミスしているケースや昔の技術のまま最新事例を見ないで話を進める事例を多数目撃した)。本年も、製品分解シリーズを楽しみにしていただきたい。

関連記事

2024年は「エッジAIデバイス元年」 主要AI PCを分解

2024年は「エッジAIデバイス元年」 主要AI PCを分解

さまざまなモバイル機器で、AI(人工知能)機能は既に必須になりつつある。特に2024年はAI PCが相次いで市場に投入され、「エッジデバイスAI元年」とも呼べるほどである。今回は、2024年後半に発売された主要AI PCやプロセッサを取り上げよう。 それでもスマホの技術進化は続いている、「iPhone 15 Pro Max」「Mate 60 Pro」を分解

それでもスマホの技術進化は続いている、「iPhone 15 Pro Max」「Mate 60 Pro」を分解

今回は、2023年夏に発売された話題のスマートフォン、Apple「iPhone 15 Pro Max」とHuawei「Mate 60 Pro」の分解結果を報告する。 NVIDIAもIntelも……チップ開発で進む「シリコン流用の戦略」を読み解く

NVIDIAもIntelも……チップ開発で進む「シリコン流用の戦略」を読み解く

プロセッサでは、半導体製造プロセスの微細化に伴い、開発コストが増大している。そこで半導体メーカー各社が取り入れているのが、「シリコンの流用」だ。同じシリコンの個数や動作周波数を変えることで、ローエンドからハイエンドまでラインアップを増やしているのである。 「S9」のベースは「A16 Bionic」!? Appleの自在過ぎるスケーラブル戦略

「S9」のベースは「A16 Bionic」!? Appleの自在過ぎるスケーラブル戦略

Appleのプロセッサ開発力は、スピードを含め確実に上がっている。さらにAppleは、コア数を自由自在に増減し、ローエンドからスーパーハイエンドまでのプロセッサファミリーをそろえる「スケーラブル戦略」を加速している。発売されたばかりの「Apple Watch Series 9」を分解すると、それがよく分かる。 「Copilot+ PC」を分解 際立つQualcommのスタートダッシュ

「Copilot+ PC」を分解 際立つQualcommのスタートダッシュ

2024年6月、「Copilot+ PC」が各社から一斉に発売された。今回、テカナリエは「Surface Laptop(第7世代)」を分解。ひと際目立っていたのが、真っ先にCopilot+ PCに対応したQualcommのチップセットだ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

Special SitePR

あなたにおすすめの記事PR