ケイデンス、チップレット開発期間の短縮に向けエコシステム構築:開発リスクを軽減し市場投入を加速

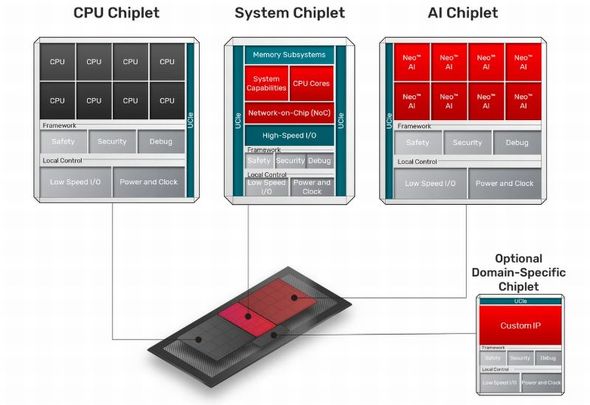

ケイデンスは、フィジカルAIやデータセンター、高性能コンピューティング(HPC)などに向けたチップレットの開発期間を短縮するための「パートナーエコシステム」を発表した。Samsung FoundryやArmらと協業し、Cadence Physical AIチップレットプラットフォームをベースとした「事前検証済みチップレットソリューション」を提供していく。

パートナーIPをSamsung FoundryのSF5Aプロセス上で事前に統合

ケイデンスは2026年1月、フィジカルAIやデータセンター、高性能コンピューティング(HPC)などに向けたチップレットの開発期間を短縮するための「パートナーエコシステム」を発表した。Samsung FoundryやArmらと協業し、Cadence Physical AIチップレットプラットフォームをベースとした「事前検証済みチップレットソリューション」を提供していく。

ケイデンスが提供する「Chiplet Spec-to-Packaged Partsエコシステム」は、チップレット開発における設計の複雑さを軽減することによって、リスクを軽減し市場投入までの期間を短くすることを狙いとしている。IP(Intellectual Property)を提供する初期パートナーとしてはArmやArteris、eMemory、M31 Technology、Silicon Creations、Trilinear Technologiesが、半導体解析技術のパートナーとしてはproteanTecsが、それぞれ参加を表明している。

またSamsung Foundryと協力し、パートナーが提供するIPをSF5Aプロセス上で事前に統合した「Cadence Physical AIチップレットプラットフォーム」をベースとする半導体試作のデモを構築する。

パートナーであるArmとは、これまでの協業関係をさらに拡大し、フィジカルAIやインフラAI分野における技術革新を加速させていく。このため、Arm Zena Compute Subsystem(CSS)やその他の主なIPを活用し、Physical AIチップレットプラットフォームやChiplet Frameworkを強化していく。

ケイデンスが提供するチップレットソリューションを活用すれば、「Cadence Xcelium Logic Simulator」によるシミュレーションと、「Cadence Palladium Z3 Enterprise Emulation Platform」によるエミュレーションをシームレスに実行できる。また、リアルタイムフィードバックにより、配置配線プロセスを効率よく行うことが可能となる。

しかも、生成されたチップレットアーキテクチャは、「Arm Chiplet System Architecture」や、今後策定される見通しの「OCP Foundational Chiplet System Architecture」といった標準に準拠している。このため、広範な相互運用性を確保できるという。さらに、ケイデンスが提供するUCIe IPによって、業界標準のダイ間接続を実現。PCIe 7.0やHBM4など先端インタフェースの統合も迅速に行うことができる。

関連記事

CadenceがHexagonの設計&エンジニアリング事業を買収へ

CadenceがHexagonの設計&エンジニアリング事業を買収へ

Cadence Design Systemsが、スウェーデンのソフトウェアメーカーHexagonの設計&エンジニアリング(D&E)事業を31億6000万米ドルで買収すると発表。マルチフィジックスシミュレーション分野でさらなる大きな一歩を踏み出した。 トヨタやルネサスなど12社、車載用SoC開発に向け新組織「ASRA」を設立

トヨタやルネサスなど12社、車載用SoC開発に向け新組織「ASRA」を設立

トヨタ自動車やデンソー、ルネサス エレクトロニクスなど自動車メーカー、電装部品メーカー、半導体関連企業12社が、「自動車用先端SoC技術研究組合(Advanced SoC Research for Automotive/ASRA)」を2023年12月1日付で設立した。チップレット技術を適用した車載用SoC(System on Chip)の研究開発を行う組織で、2030年以降の量産車に搭載すべく、研究開発を進める。 AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

AIで半導体設計時間を半減 Rapidusの2nm向け支援ツール

Rapidusは2025年12月17日、同社2nm製造プロセス向けの半導体設計支援ツール群「Raads」を発表した。2026年から順次リリース予定で、設計期間の50%短縮と、設計コストの30%削減が可能だとしている。 NVIDIAがSynopsysに20億ドル投資 EDAツールに何をもたらすのか

NVIDIAがSynopsysに20億ドル投資 EDAツールに何をもたらすのか

NVIDIAがSynopsysに2億米ドルを投資すると発表した。半導体設計やシミュレーション、検証の高速化や高精度化、低コスト化を加速させるという。両社の協業はEDAツールに何をもたらすのだろうか。 Synopsysの大量解雇は「AI設計時代」の序章なのか

Synopsysの大量解雇は「AI設計時代」の序章なのか

Synopsysが、Ansysとの合併を進める最中に10%の人員削減を実施した背景には、設計のオートメーションとAI適用があるのだろうか。 いよいよ来るか? 半導体設計/検証に「エージェントAI」

いよいよ来るか? 半導体設計/検証に「エージェントAI」

エージェント型AIを手掛ける米新興のChipAgentsが、シリーズA投資ラウンドで2100万米ドルを調達した。エージェントAIを、半導体設計/検証に浸透させるべく取り組む。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増