インテルとマイクロン、384Gビット容量の3D NANDを発表――年内量産へ:容量はサムスン、東芝の3倍!

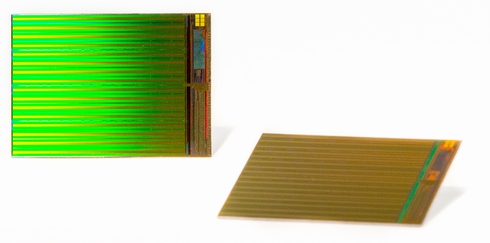

インテルとマイクロン テクノロジーは2015年3月26日(米国時間)、1ダイで384Gビット容量を実現した3次元積層構造を用いたNAND型フラッシュメモリ(以下、3D NAND)を共同開発したと発表した。

32層構造

インテルとマイクロン テクノロジーは2015年3月26日(米国時間)、1ダイで384Gビット容量を実現した3次元積層構造を用いたNAND型フラッシュメモリ(以下、3D NAND)を共同開発したと発表した。同日、256Gビット品のサンプル出荷を開始し、2015年夏までに384Gビット容量品のサンプル出荷を開始するという。量産は2015年内を予定している。

開発した3D NANDは、メモリセルを垂直方向に32層、重ねた構造を採用。セル当たり2ビットのデータを記憶するMLC(マルチレベルセル)で256Gビット、同3ビットのデータを記憶するTLC(トリプルレベルセル)で384Gビットの容量を実現したという。

フローティングゲートを採用

メモリセル構造には、従来の平面構造NANDにも採用してきたフローティング・ゲート・セル構造を採用し、同構造を用いたことが「設計上の大きな鍵となっており、これにより性能や品質、信頼性の向上が可能になった」(両社)とする。

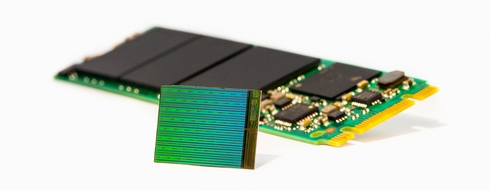

「競合するNANDの3倍の容量」(両社)とする最大384Gビットの容量を実現したことにより、「板ガムサイズのSSDで3.5Tバイト以上、標準的な2.5インチSSDで10Tバイト以上のストレージ容量を搭載することが可能になる」とし、2016年以降にSSD製品の量産出荷も開始するという。

東芝、サムスンは128Gビット

メモリセルを垂直方向に積層し、面積当たりの記録密度を高める3D NANDは、2013年には、サムスン電子がチャージトラップフラッシュ(CTF)技術を用いた24層構造の128Gビット容量の3D NANDを世界で初めて製品化。サムスンは翌2014年にも、32層構造の3D NAND(128Gビット容量/TLC品)を製品化し先行。また東芝も2015年3月26日(日本時間)に、「BiCS」と呼ぶ3次元積層構造を用いた3D NANDのサンプル出荷を開始。サムスンを上回る48層構造ながら、容量はMLCで、128Gビットだった。

関連記事

東芝、3次元NAND「BiCS」の製品化を発表――サムスン上回る48層構造

東芝、3次元NAND「BiCS」の製品化を発表――サムスン上回る48層構造

東芝は2015年3月26日、「BiCS」と呼ぶ3次元積層構造を用いたNAND型フラッシュメモリ(以下、3D NAND)を開発し、同日サンプル出荷を開始したと発表した。 サムスンの3次元NAND、3ビット/セルの128G品が出荷間近

サムスンの3次元NAND、3ビット/セルの128G品が出荷間近

Samsung Electronics(サムスン電子)が2013年に発表した、3次元構造のNANDフラッシュメモリ「V-NAND」。3ビット/セルの128Gビット品を、間もなく出荷する予定だという。2015年には、256Gビット品も発表できるとしている。 サムスン電子が「業界初」の3次元NANDを量産

サムスン電子が「業界初」の3次元NANDを量産

Samsung Electronics(サムスン電子)は、メモリセルを垂直に積層した3次元セル構造のNAND型フラッシュメモリの量産を発表した。記憶容量は128Gビットで、セルの積層数を増やすなどすれば、将来的には1テラビット容量も可能だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める