EE Times Japan >

プロセス技術 >

ARMから見た7nm CMOS時代のCPU設計(7)〜CPUコアの性能をレイアウトが大きく左右:福田昭のデバイス通信(18)(2/2 ページ)

» 2015年04月09日 09時30分 公開

[福田昭,EE Times Japan]

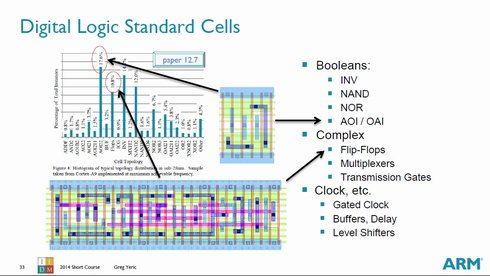

回路の変更でトランジスタ数を減らす

実際のCPUコアは、さまざまなスタンダードセルで構成されている。当然ながら、よく使われるセルと、あまり使われないセルが存在する。ARMがCortex-A9コアでスタンダードセルごとの使用率を調べたところ、全体の中で最も多く使われたのは「AOI22(2入力2出力のAND-OR-INV)」ゲートで、17.6%を占めた。次が「INV」ゲートで14%、その次が「NAND2(2入力NAND)」ゲートで12.0%を占めた。4番目に多かったのは「フリップフロップ」で、10.8%となっていた。使用率が10%を超えたのは、これら4種類のセルだけである。

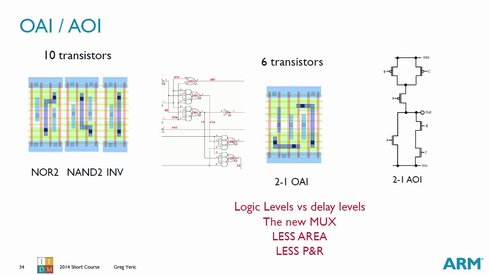

ここで重要なのは、回路の工夫によって比較的複雑なスタンダードセルのシリコン面積を減らすことである。例えば2入力1出力のOAI(OR-AND-INV)ゲートは、単純に考えるとNORとNAND、INVの組み合わせでレイアウトすることになる。このときのトランジスタ数は10個である。これを回路の変更により、6個のトランジスタで実現する。するとシリコン面積が減り、遅延時間は短くなり、配置・配線工程の作業が減る。回路レベルでトランジスタ数を減らしておくことは、性能向上とコスト削減に非常に大きな効果をもたらす。

(次回に続く)

関連記事

電池もウェアラブルな時代に? SELが曲がるバッテリを披露

電池もウェアラブルな時代に? SELが曲がるバッテリを披露

半導体エネルギー研究所(SEL)が、“曲がるリチウムイオン二次電池”を展示した。容量は300mAhほどだが、手首に巻き付けられるくらいに曲げることができる。実用化するには、まずは安全性を高めたいとしている。 ウェアラブル製品の台頭で、存在感増すヘルスケア分野

ウェアラブル製品の台頭で、存在感増すヘルスケア分野

「2014 International CES」の主役の1つは、何と言ってもウェアラブル機器だった。そのターゲット市場として最も大きな分野の1つはヘルスケアやフィットネスである。2014 CESでも、多くのメーカーが、これらの分野向けにさまざまなウェアラブル製品を展示した。 開発メーカーに聞きたい、なぜ“ウェアラブル”なのか?

開発メーカーに聞きたい、なぜ“ウェアラブル”なのか?

続々と市場に投入されるウェアラブル機器。大手電機メーカーも相次いでウェアラブル製品を発表している。しかし、ウェアラブル、つまり“身に着けられる”ことが「ユーザーにとって一番の利点」だと本当に考えて製品を開発しているメーカーは、どれだけあるのだろうか。 やがては飽きる? ウェアラブル機器

やがては飽きる? ウェアラブル機器

2014年の大きなトレンドの1つは、間違いなくモノのインターネット(IoT)やウェアラブル機器だろう。だが筆者は、自分の脈拍や睡眠パターンをいちいち測定されることに、いまいち喜べない。 ウェアラブル機器やIoTが生活を変え、5Gや微細化技術が世界を驚かす

ウェアラブル機器やIoTが生活を変え、5Gや微細化技術が世界を驚かす

2014年は、どんな技術革新が世界を驚かせるのだろうか? ウェアラブル機器、IoT、5Gなど「2014年に注目すべき10の技術」を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

Special SitePR

あなたにおすすめの記事PR