「FinFET対FD-SOI」の構図はなくなる? いずれは共存へ:プロセス技術

FinFETとFD-SOI(完全空乏型シリコン・オン・インシュレータ)の両方の技術を、用途などに合わせて採用しようと考える半導体メーカーが増えているという。ファウンドリ側も、こうしたニーズに柔軟に対応することが必要になってくる。

ほとんどの半導体メーカーは、FinFETか、FD-SOI(完全空乏型シリコン・オン・インシュレータ)のどちらかを採用している。ただし、GLOBALFOUNDRIES、Samsung Electronicsなどのファウンドリは、顧客企業に対して両方の技術を提供しなければならないだろう。両方のプロセスの使用を検討するチップメーカーも増えている。

例えば、Freescale SemiconductorがEE Timesに明かしたところによると、同社は高速かつ低消費電力なチップを実現するために、14nm〜16nmノードにはFinFET技術を、28nmノードにはFD-SOIを適用しているという。ただし、両製品はまったく別の分野に向けたものになる。

IBMやSoitec、Freescale Semiconductorなどが参画するSOI Industry Consortiumは、SOIウエハー上にFinFETを構築する技術を階はsつしている 出典:SOI Industry Consortium

IBMやSoitec、Freescale Semiconductorなどが参画するSOI Industry Consortiumは、SOIウエハー上にFinFETを構築する技術を階はsつしている 出典:SOI Industry Consortium用途に合わせて、適切なプロセスを選ぶ

Freescaleのマイコン(MCU)グループでアプリケーションプロセッサ/最先端技術担当バイスプレジデントを務めるRon Martino氏は、EE Timesに対して、「Freescaleは、あらゆるファウンドリと提携し、比較的単純な技術から複雑な技術まで幅広いプロセス技術を適用した製品を扱っている。その多くは当社が独自に開発した技術だ。結果的に当社は、FinFETとFD-SOIの両方に最適化したロードマップを開発してきたことになる。例えば、FD-SOIウエハーは高コストだが、28nmのアプリケーションプロセッサ『i.MX』の消費電力と性能の両方を強化できる。一方、デジタルネットワーキング向け製品の場合、成功のカギを握るのはFinFETだ」と説明している。

「FD-SOIは、センサーの統合を必要とするチップに適している。当社の28nm FD-SOIチップはRFとアナログ機能を備え、ウェアラブル製品に求められる接続性と低消費電力の両方をバランスよく実現している。40nmと28nmにはFO-SOI、14nm〜16nmのような最先端ノードにはFinFETといったように、ノードによって最適なプロセス技術は異なる。微細化やコストの最適化の実現は、われわれがFD-SOIとFinFETをいかに効率的に採用するかにかかっている」(Martino氏)。

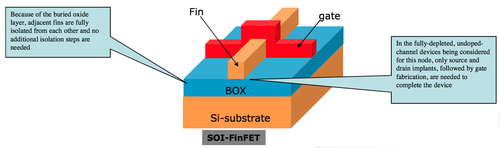

ST Microelectronicsは、FinFETではなくFD-SOIを採用してきた。「FD-SOIは、トランジスタの下に埋め込み酸化膜(BOX)を形成する。トランジスタチャネルが実装されたシリコン膜は非常に薄く、チャネルドーピングが不要になるので、トランジスタを完全空乏型にすることができる。それによってリーク電流を最小限に抑えられる」と説明している。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

GLOBALFOUNDRIES、22nm FD-SOIプロセスでの製造を2016年に開始か

GLOBALFOUNDRIES、22nm FD-SOIプロセスでの製造を2016年に開始か

GLOBALFOUNDRIESは、22nm FD-SOI(完全空乏型シリコン・オン・インシュレータ)プロセスの導入について、2016年末の量産開始を目指すという。同社は「28nm FinFETと同程度のコストで、14nm FinFETと同等の性能を実現できる」としている。 CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に

IBMがIII-V族化合物半導体を使ったFinFETの開発成果を積極的に発表している。IBMは、局所横方向エピタキシャル成長(CELO)技術により、シリコンおよびSOI基板の両方に、通常のCMOSプロセスで、InGaAsのFinFETを形成したと発表した。 「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

「ムーアの法則は間もなく終えんを迎える」、BroadcomのCTOが語る

BroadcomのCTO(最高技術責任者)が、「ムーアの法則はあと15年ほどで終えんを迎える。半導体プロセスの微細化は、5nm以降はほぼ進歩しない」という見解を示した。 ムーアの法則、50年をたどる

ムーアの法則、50年をたどる

1965年、IntelのGordon Moore(ゴードン・ムーア)氏が雑誌に掲載したトランジスタに関する予見は、「ムーアの法則」として半導体技術の発展の大きな原動力となった。ムーアの法則によってトランジスタがどれほど進化してきたのか。50年を振り返ってみる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

FreescaleのRon Martino氏

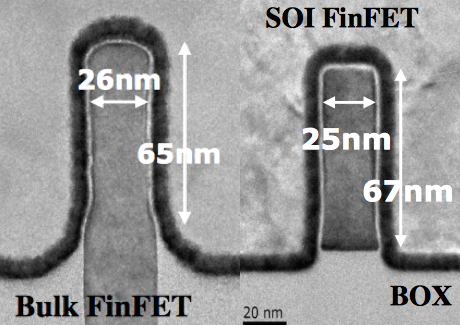

FreescaleのRon Martino氏 SOI上に形成したFinFET 出典:SOI Industry Consortium

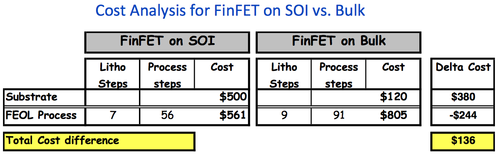

SOI上に形成したFinFET 出典:SOI Industry Consortium SOIウエハー上のFinFETと、バルクシリコン上のFinFETについて、コストを比較したもの。SOIの方がやや高い 出典:SOI Industry Consortium

SOIウエハー上のFinFETと、バルクシリコン上のFinFETについて、コストを比較したもの。SOIの方がやや高い 出典:SOI Industry Consortium