NVIDIAのGPU不足は今後も続く ボトルネックはHBMとTSMCの中工程か:湯之上隆のナノフォーカス(72)(6/6 ページ)

HBMを巡るDRAMメーカーの争い

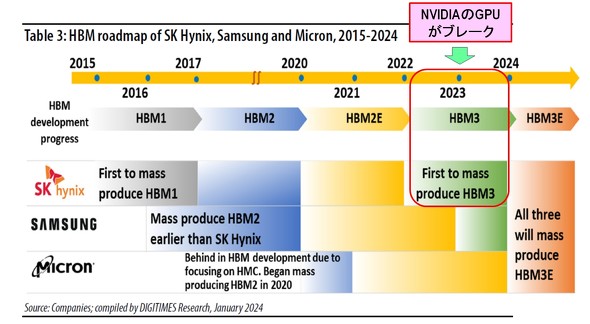

図16は、2015〜2024年において、DRAMメーカー3社が、どのようにHBMを生産してきたかを示している。

図16 SK hynix、Samsung、MicronのHBMのロードマップ[クリックで拡大] 出所:DIGI TIMES Research, ”HBM Technology and capacity development” (2024年1月)のレポートの図

図16 SK hynix、Samsung、MicronのHBMのロードマップ[クリックで拡大] 出所:DIGI TIMES Research, ”HBM Technology and capacity development” (2024年1月)のレポートの図最初にHBM1の量産に成功したのは、SK hynixである。とろろが、HBM2では、SK hynixよりも、Samsungの方が先に量産を実現した。そして、2023年にNVIDIAのGPUが大ブレークしたとき、たまたま(?)SK hynixがどこよりも早くHBM3の量産に成功した。これが、SK hynixに多大な利益をもたらした。その結果、DRAMのチャンピオンのSamsungは後れを取ってしまった。

一方、もう1社のDRAMメーカーのMicronは、当初HBMとは規格が異なるHMC(Hybrid Memory Cube)の開発を行っていた。しかし、米国で半導体標準化を推進する業界団体JEDEC(Joint Electron Device Engineering Council)が、HMCではなく、HBMの規格を正式に認定した。そのため、Micronは2018年以降、HMCの開発を諦め、韓国メーカー2社に大きく遅れてHBMの開発に参入することになった。

以上の結果、2024年3月20日のBloombergの報道によれば、HBMの市場シェアは、SK hynixが54%、Samsungが41%、Micronが5%となっている。

HBMのシェア1位のSK hynixは、2023年にNANDの工場M15でHBMの生産を開始した。また、ことし2024年前半にHBM3Eをリリースする。さらに、2025年には、現在建設中のM15X工場をHBM専用に設計変更し、HBM3EとHBM4を生産する予定である。

一方、SK hynixに追い付きたいSamsungは、2023年にSamsung Displayの工場でHBMの生産を開始し、2024年にはHBMのキャパシティーを2倍に拡大し、2025年にはSK hynixより早くHBM4を量産する計画を立てている。

出遅れてしまったMicronは、HBM3をスキップし、2024〜2025年にHBM3Eで勝負をかけ、2025年に市場シェア20%を獲得することを目指している。さらに2027〜2028年にかけて、HBM4およびHBM4Eの量産で、先行する韓国メーカー2社に追い付く目標を立てている。

このように、DRAMメーカー3社が激しい競争を展開することによって、HBMの出荷個数が飽和する状態を打破し、それがHBM不足を解消することにつながるかもしれない。

NVIDIAのGPU不足はいつまで続くのか

本稿では、NVIDIAのGPUなどのAI半導体が世界的に不足している原因について説明してきた。その原因は以下の2つである。

1)NVIDIAのGPUは、TSMCのCoWoSパッケージで作られている。このCoWoSのキャパシティーが全く足りない。その理由は、GPU、CPU、HBMなどのチップを搭載するシリコンインターポーザーが、世代が進むとともに巨大化していることにある。TSMCはこの中工程のキャパシティーを増大しようとしているが、GPUの世代が進むとインターポーザーも巨大化するため、いつまでも「いたちごっこ」が続く可能性がある。

2)CoWoSに搭載されるHBMが不足している。その理由は、DRAMメーカーは1nm刻みで微細化を続けなければならない上に、HBMの規格も2年間隔で世代交代を余儀なくされ、HBMの中に積層するDRAMチップも世代とともに増大するからである。DRAMメーカーは全力でHBMを生産しているが、その出荷個数は2025年以降、飽和すると予測されている。ただし、HBMの価格が非常に高いことから、DRAMメーカーが猛烈な競争を展開しており、その結果としてHBM不足を解消する可能性も考えられる。

このように、NVIDIAのGPU不足をもたらしているボトルネックは、TSMCの中工程のキャパシティー不足とHBM不足の2つあるが、これらの問題が1年程度で解決されるとは考えにくい。従って、NVIDIAのGPU不足は、今後数年(いや、もっとか?)は続くと予測する。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。2023年4月には『半導体有事』(文春新書)を上梓。

関連記事

半導体の好況は「NVIDIAのGPU祭り」による錯覚? 本格回復は2025年以降か

半導体の好況は「NVIDIAのGPU祭り」による錯覚? 本格回復は2025年以降か

半導体の世界市場は2023年に底を打ち、2024年には本格的な回復基調に乗ると見られていた。だが、どうもそうではないようだ。本稿では、半導体の市況が回復しているように“見える”理由を分析するとともに、TSMCなどのファウンドリーの稼働状況から、本当の市場回復が2025年にずれ込む可能性があることを指摘する。 2024年の半導体市場、本格回復はメモリ次第 〜HBMの需要増で勢力図も変わる?

2024年の半導体市場、本格回復はメモリ次第 〜HBMの需要増で勢力図も変わる?

半導体市場の本格的な回復が予想されている2024年。鍵を握るのがメモリだ。本稿では、DRAM/NAND型フラッシュメモリの価格推移と企業別売上高の動向から、半導体市場の回復基調の時期を探る。さらに、そこから読み取れる、メモリメーカーの“栄枯盛衰”を示す。 imecも全幅の信頼、Rapidusの「成功の定義」とは何か

imecも全幅の信頼、Rapidusの「成功の定義」とは何か

imecや経済産業省など、Rapidusの支援を公言する組織/企業は多い。さらに、米TenstorrentやフランスLetiなど、Rapidusとパートナーシップを締結する企業や機関も増えている。それはなぜなのか。2023年11月に開催された「ITF(imec Technology Forum) Japan」で見えてきたその理由と、Rapidusにとっての「成功の定義」をあらためて考えてみたい。 史上最悪レベルの半導体不況に回復の兆し、生成AIという新たな“けん引役”も

史上最悪レベルの半導体不況に回復の兆し、生成AIという新たな“けん引役”も

“コロナ特需”から一転、かつてないレベルの不況に突入した半導体業界だが、どうやら回復の兆しが見えてきたようだ。本稿では、半導体市場の統計や、大手メーカーの決算報告を基に、半導体市場の回復時期を探る。さらに、業界の新たなけん引役となりそうな生成AIについても言及する。 裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023

裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023

2023年6月に開催された「VLSIシンポジウム2023」は大盛況であった。本稿では、筆者が“ブレークの予感”を抱いた裏面電源供給技術と、3D(3次元) NAND/DRAM技術に焦点を当てて、解説する。 日本の前工程装置のシェア低下が止まらない 〜一筋の光明はCanonの戦略

日本の前工程装置のシェア低下が止まらない 〜一筋の光明はCanonの戦略

筆者は2022年7月のコラムで、日本の前工程装置の世界シェアが、2010年から2021年にかけて急落していることを報告した。2022年もその状況は改善されていない。だが、露光装置には、一筋の光明を見いだせそうである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- 東芝との協議やデンソー提案への対応、ロームが新声明

- デンソー、ロームに対する株式取得提案を正式表明

- キオクシアが超高IOPS SSD開発 NVIDIA Storage-Nextに対応

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- STが「中国製STM32」量産開始、供給網を現地完結

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表