番外編 電源フィルタの設計に悪戦苦闘、雑音を抑えるはずが発振状態に…(前編):Analog ABC(アナログ技術基礎講座)(4/4 ページ)

アンプ自身が雑音を生む

どの程度、VCC2が揺すられるかを知るために、電流源I1を信号源として交流(AC)解析を実施してみました。その結果、VCC2は5MHz付近で最も利得が高くなり、値は約48.9dB(278倍)となりました。

278倍という値は、何を意味しているのでしょうか。電流源I1において周波数が5MHzの信号が1A変化したと仮定すると、1Aの278倍もの電圧がVCC2に発生することになります。少なくとも、電源の雑音が100mVを超えるとアンプが誤動作してしまうことを考慮すると、許される電流源I1の変化量は、100mV/278=360μAになります。

今回のアンプ全体のバイアス電流は18mAであることを考えると、消費電流の変化がわずか360μAということはありえません。少なくとも、ピークトゥーピーク値で10mA程度の変化があるはずです。ということは、電源フィルタが並列共振するために、アンプ自身の消費電流で電源雑音を作ってしまっていることになります。

ダンピング抵抗で並列共振を抑制

並列共振の鋭さ(Q値)を下げるために、ダンピング抵抗を入れる方法があります。図3(b)にダンピング抵抗を入れた電源フィルタを示しました。

ダンピング抵抗を入れることで、共振のQ値が下がり、アンプ自身の消費電流変化によって、電源電圧が大きくゆすられることはなくなります。ダンピング抵抗を1Ωにすると、電流源I1に許される変化量は、100mV/1Ω=100mAになります。バイアス電流が18mAのアンプにとっては十分な許容量です。

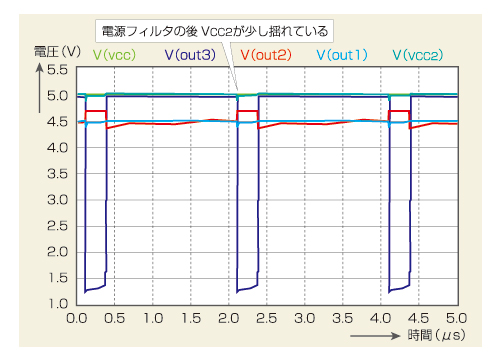

図3(b)のようにダンピング抵抗を入れたときの出力信号の波形を図4に示しました。まだ、うまくいきません…。図2(b)のように入力した信号に対して別の信号が勝手に出てくるような発振状態にはなっていないようです。その点では、ダンピング抵抗の効果が表れています。

図4 電源フィルタにダンピング抵抗を入れた後の出力波形 ダンピング抵抗を入れることで、電源フィルタの共振は十分に抑えたはずです。ところが、VCC2がまだ少しゆれてしまい、出力信号Vout3がパルス状に変化してしまっています。

図4 電源フィルタにダンピング抵抗を入れた後の出力波形 ダンピング抵抗を入れることで、電源フィルタの共振は十分に抑えたはずです。ところが、VCC2がまだ少しゆれてしまい、出力信号Vout3がパルス状に変化してしまっています。しかし、電源に雑音が載るたびに、大きなパルスが出力されてしまい、正しい動作をしていません。VCC2がまだ少しゆれてしまっているようです。電源フィルタの共振は十分に抑えたはずなのに、どこがまずいのでしょうか…。

1回分でアンプの電源フィルタの紹介を終える予定でしたが、予想以上にひどく発振しているので、アンプをまともに動かせるようになるか少々心配です。次回も、悪戦苦闘の続きを紹介します。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- ソニー半導体、26年度は減収見込み メモリ市況不透明