動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?:プロセス技術(2/2 ページ)

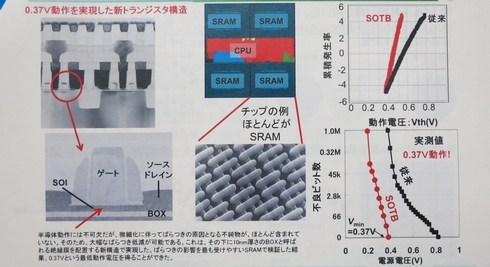

SOTBを用いた2MビットSRAMの0.37V動作を実証

ロジック回路の消費電力を削減するには、CMOSトランジスタの動作電圧を下げるのが有効な方法の1つだが、従来のバルクCMOSでは、微細化に伴って動作特性にばらつきが生じていた。今回、シリコン基板上に10nm厚のBOXと呼ばれる絶縁膜を配置したSOTB上にトランジスタを形成することにより、しきい値電圧のばらつきを0.2〜0.3Vに抑え込むことに成功した。この新型トランジスタを用いて2MビットSRAMを試作して検証したところ、最低0.37Vでの動作を確認した。

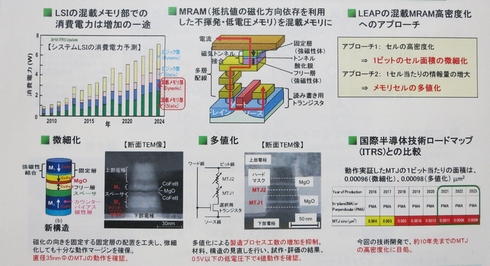

磁性変化デバイス(MRAM)の大容量化技術

磁性変化デバイス(MRAM)の大容量化技術として、「微細化による高密度化を実現できるスピン注入型(STT)MRAM」と「高密度化を実現できる4値/セルのSTT-MRAM」の2件を発表した。これらの技術はCPUに混載するキャッシュメモリ向けに開発されたものである。

微細化しても安定したメモリ動作を可能とするSTT-MRAM技術では、磁化の向きを固定する固定層の配置を工夫し、微細化しても十分な動作マージンが確保できるような構造とした。直径35nmのMTJ(Magnetic Tunnel Junction)を試作し、データ保持性能を評価したところ、微細プロセスによる製造ばらつきの影響が軽減されて、安定したメモリ動作を確認できたという。

一方、大容量化に向けた4値/セル構造のSTT-MRAM技術は、2つのメモリ素子を単純に積層して、それを一括エッチングで加工するメモリ構造と製造プロセスを開発した。直径50nmのメモリ素子を試作し評価したところ、0.5V以下の電源電圧で4値の動作を確認できたという。

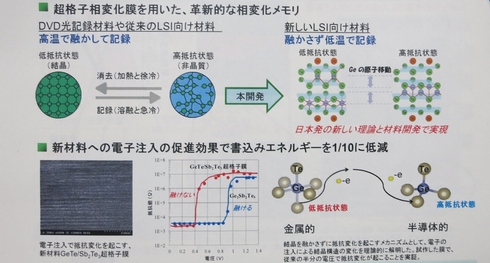

相変化デバイス(PCM)の低消費電力技術

新開発のPCM技術は、データセンターで用いられるSSD(Solid State Drive)向けなどに開発した。SSDに搭載されている現行のフラッシュメモリでは、高い内部電圧が必要なことやデータを高速伝送するのに消費電力が大きくなるなどの課題があった。抵抗変化でデータを保持するPCMは、次世代メモリとして注目されているが、データを記録/消去するために結晶を加熱/冷却して、抵抗状態を変える必要があった。そこで今回、結晶を融かさずに抵抗変化を起こすメカニズムとして、電子注入による結晶構造の変化を理論的に解明した。また、電子注入で抵抗変化を起こす新材料「GeTe/Sb2Te3超格子膜」を開発した。この材料を使って検証を行ったところ、従来のPCMに比べて書き込みの消費電力を1/10に削減することが可能となったという。

結晶を融かさずに抵抗変化を起こすメカニズムの解明と電子注入で抵抗変化を起こす新材料の開発で、従来に比べて書き込み消費電力を1/10に削減することが可能となった新開発のPCM (クリックで拡大) 出典:NEDO、LEAP

結晶を融かさずに抵抗変化を起こすメカニズムの解明と電子注入で抵抗変化を起こす新材料の開発で、従来に比べて書き込み消費電力を1/10に削減することが可能となった新開発のPCM (クリックで拡大) 出典:NEDO、LEAP小型化を可能とする金属原子移動型スイッチデバイス

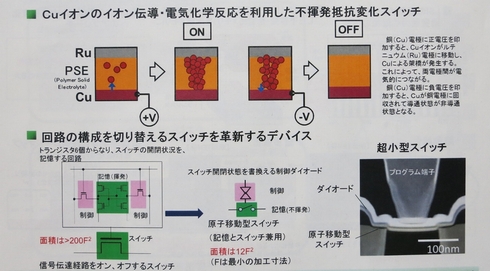

金属電子移動型スイッチデバイスは、LSIの銅配線間に組み込むことで、回路の構成を切り替える機能を持たせることができる。この機能を使えばLSIの再構成や機能変更を電気的に行うことができる。しかし、スイッチデバイスを使った再構成回路には、それをプログラミングするための選択トランジスタを組み合わせて使う必要がある。この選択トランジスタがチップサイズを小型化するのに妨げとなっていた。

今回開発した技術は、多層銅配線内に形成した酸化タンタルからなるダイオードを選択素子として用いても、電子移動型スイッチのプログラミングが可能であることを実証した。これによって、回路構成を切り替えるスイッチ部の占有面積は、これまで選択トランジスタを使っていた場合、最大200F2(Fは最小の加工寸法)必要だった。今回開発した技術を用いることで、12F2に小型化ができる可能性を示した。

多層銅配線内に形成した酸化タンタルからなるダイオードを選択素子として用いても、電子移動型スイッチのプログラミングが可能なことを実証した。これにより、スイッチ部の占有面積を12F2に小型化ができる(クリックで拡大) 出典:NEDO、LEAP

多層銅配線内に形成した酸化タンタルからなるダイオードを選択素子として用いても、電子移動型スイッチのプログラミングが可能なことを実証した。これにより、スイッチ部の占有面積を12F2に小型化ができる(クリックで拡大) 出典:NEDO、LEAP研究成果の発表に先立って、NEDOで電子・材料・ナノテクノロジー部の主任研究員を務める吉田学氏より、NEDOが取り組んでいる「低炭素社会を実現する超低電圧デバイスプロジェクト」(実施期間は平成22〜26年度)について、その目的などが紹介された。研究開発の委託先となるLEAPには半導体関連企業10社が参加している。再委託先の主要大学も含めた研究チームで、IT機器の消費電力を1/10に削減できるデバイスの早期開発を目指している。吉田氏は、「単に各デバイスの特性を向上させるためのプロジェクトではない。『電池レスのモバイルコミュニケーションが作る、快適、安全、安心社会』を実現するために、未来のアプリケーションを想定して、デバイスの研究開発に取り組んでいる」と述べた。

- MSがWindowsのAI統合戦略を転換、パフォーマンスと信頼性向上に注力/Armが自社設計のCPU「Arm AGI CPU」を発表

- TDK、Apple向けTMRセンサーを初めて米国で生産へ

- PR:自動車と産機を軸に成長加速へ、データセンター用電源が追い風に STマイクロエレクトロニクス

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- マスク氏、次世代半導体工場「Terafab」発表 計算リソースは宇宙空間へ

- 「Steam Machine」などは2026年内発売に? 一方でSteam Deck OLEDは値上げ/Microsoftが新プラン「Microsoft 365 E7」を提供開始

- 目指すは500nm RDL 太陽HDがimecと挑む次世代パッケージング材料

- キヤノンと日本シノプシスがRapidusに委託へ

- AI PCでクラウド×ローカルの「ハイブリッドAI」実現

- ローム、TSMCライセンス受けGaN一貫生産へ 27年目標

関連記事

EVとCHAdeMO方式の急速充電器を導入、NEDOがスペインで実証実験

EVとCHAdeMO方式の急速充電器を導入、NEDOがスペインで実証実験

NEDOは、スペイン・マラガ市で日本製の電気自動車(EV)160台とCHAdeMO方式の急速充電器23口を配置し、「スマートコミュニティ」の実証実験を始める。この実証プロジェクトで得られた技術や成果を活用し、今後は欧州の他の国や中南米地域に対してもシステムの事業展開を行っていく。 いよいよSiCの時代へ、業界初の「フルSiCパワーモジュール」が量産

いよいよSiCの時代へ、業界初の「フルSiCパワーモジュール」が量産

ロームは、パワーモジュールを構成するパワーMOSFETとショットキーバリアダイオード(SBD)に全てSiC材料を採用した品種の量産を開始する。独自の信頼性向上技術を開発することで量産体制を確立した。 ITOを用いない透明導電膜、有機EL照明/テレビの低価格化の鍵に

ITOを用いない透明導電膜、有機EL照明/テレビの低価格化の鍵に

高価な材料であるITOを使わない透明導電膜を実用化できれば、有機EL照明や有機ELテレビの低価格化に大いに貢献するだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

NEDOで電子・材料・ナノテクノロジー部の主任研究員を務める吉田学氏

NEDOで電子・材料・ナノテクノロジー部の主任研究員を務める吉田学氏