データ変換器編:回路技術で急激に力を付ける韓国勢:徹底プレビュー「ISSCC2015の歩き方」(4)(2/2 ページ)

SNDRが90.4dBと高い低消費電力A-D変換技術

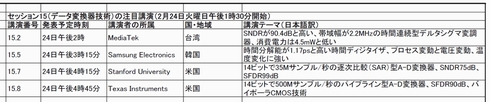

それでは、注目講演を具体的にご紹介しよう。セッション15(2月24日火曜日午後1時30分開始予定)ではまず、中国と台湾のMediaTekが共同発表する、信号対(雑音プラス歪み)の比率(SNDR:Signal to Noise and Distortion Ratio)が90.4dBと高いA-D変換技術が注目される(講演番号15.2)。変換回路のアーキテクチャは時間連続型のデルタシグマ(ΔΣ)変調器で、ループ遅延(ELD)を独自の方式で補償する。消費電力は4.5mWと低い。

時間分解能が1.17psときわめて高い時間ディジタイザ(TDC:Time to Digital Converter)も、要注目の開発成果だ。韓国のSamsung Electronicsが発表する(講演番号15.5)。2の14乗個(1万6384個)の遅延素子を内蔵し、信号遷移タイミングのばらつきを利用して統計的な処理を実施し、100Mサンプル/秒で1.17psの時間分解能を達成した。プロセス変動、電圧変動、温度変化に対して安定に動作する。電源電圧は最小0.6Vである。

エネルギー効率がきわめて高い1mWの13ビットA-D変換技術

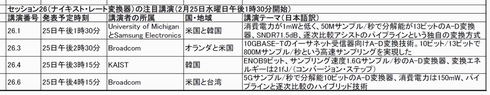

セッション26(2月25日水曜日午後1時30分開始予定)では、FOM(figure of merit)が6.9fJ/(変換ステップ)と電力エネルギー効率がきわめて高いA-D変換技術の評価が高い。米国のUniversity of Michiganと韓国Samsung Electronicsの共同発表である(講演番号26.1)。サンプリング速度は50Mサンプル/秒、分解能は13ビット。消費電力は1mWと低い。

有効ビット数(ENOB:Effective Number of Bit)が9ビットで、サンプリング速度が1.6Gサンプル/秒と高速なA-D変換技術も注目される。韓国のKAISTとSamsung Electronicsの共同研究成果である(講演番号26.4)。上位ビットをフラッシュ型でA-D変換し、下位ビットをインタリーブ逐次比較(SAR)型でA-D変換する、「FATI(Flash-Assisted Time-Interleaved) SAR」と呼ぶ方式を改良している。バックグラウンドでオフセットとスキューを較正する機能を備える。

関連記事

半導体ベンチャー企業は消えていくのか? ISSCCで討論

半導体ベンチャー企業は消えていくのか? ISSCCで討論

2014年2月9〜13日に米国で開催された「ISSCC」では、半導体企業やベンチャーキャピタルのCEO、個人投資家らが、半導体業界についてパネルディスカッションを行った。同業界は新興企業が減り、投資先もIT企業へと移っている。半導体企業は統廃合が進み、企業の数は減っていくという見方が強い。 日本の論文採択数は米国、韓国に次ぎ3位――ISSCC 2015の概要発表

日本の論文採択数は米国、韓国に次ぎ3位――ISSCC 2015の概要発表

2015年2月に開催される「ISSCC 2015」の概要が明らかになった。IoT(モノのインターネット)社会を具現化していくためのデバイス技術やシステム集積化技術などに関して、最先端の研究成果が発表される予定である。日本からは前回と同じ25件の論文が採択された。 マイクロ波でモーター駆動の絶縁電源と光カプラを不要に、パナソニック開発

マイクロ波でモーター駆動の絶縁電源と光カプラを不要に、パナソニック開発

モーター用インバータなどに使う大電力トランジスタの絶縁型ゲート駆動回路を、1/10以下に小型化できるという。駆動用PWM信号で5.8GHzの搬送波を変調し、非接触で大電力トランジスタ側に伝える。ゲート駆動回路の絶縁電源とフォトカプラが不要になり、1個の半導体チップに回路全体を集積できるようになる。 メモリ関連の論文は“量より質”にシフト

メモリ関連の論文は“量より質”にシフト

2013年2月に開催される「ISSCC 2013」では、メモリに関する論文の比率が従来よりもわずかに減少するとみられる。しかし、東芝やSanDisk、パナソニックらによるReRAMの研究開発成果の発表をはじめ、メモリ分野の論文の内容自体は、依然として魅力的だ。 第1回 最先端の半導体チップを見に行こう

第1回 最先端の半導体チップを見に行こう

毎年2月に米国のサンフランシスコで開催される半導体チップ関連の国際学会「ISSCC」。半導体のほぼ全ての分野をカバーしていて、200本の論文が発表され、約3000人が来場する。半導体業界にとって重要な学会であるISSCCについて、開催概要から分野別の注目テーマまで、徹底的にプレビューする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- 次世代パワー半導体向け接合材を開発、エレファンテック