メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目:徹底プレビュー「ISSCC2015の歩き方」(11)(3/3 ページ)

» 2015年01月19日 12時00分 公開

[福田昭,EE Times Japan]

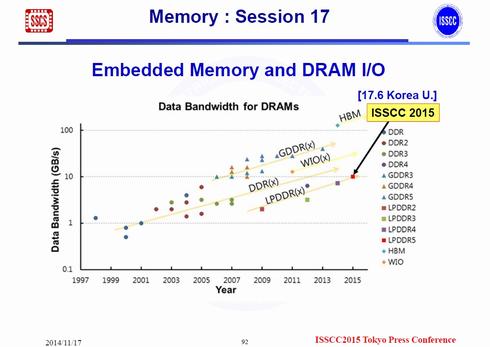

10Gビット/秒の超高速DRAMインタフェース

半導体メモリのもう1つの主役であるDRAMでは、データ転送速度の高速化と低消費電力化が最近は著しい。市販されている最新世代の汎用DRAMインタフェースはDDR3、低消費DRAMインタフェースはLPDDR3である。次世代インタフェースには、それぞれDDR4とLPDDR4が控えている。ISSCC2015では、さらにその先の低消費DRAMインタフェースである、LPDDR5の研究成果が登場する。

DRAMインタフェースの研究成果が報告されるのは、セッション17である。韓国のKorea Universityと韓国のSK Hynixが共同で、ピン当たり10Gビット/秒と高速な低消費電力DRAMインタフェース(LPDDR5)向けトランシーバ技術を公表する(講演番号17.6)。韓国のSamsung Electronicsは、ピン当たり2.67Gビット/秒のDDR4 SDRAM向けDLL技術を報告する(講演番号7.7)。4枚のシリコンダイを積層してTSV技術で相互接続するスタック・モジュール向けである。

この他、高性能プロセッサに向けたオンチップキャッシュ技術の講演がこのセッションでは相次ぐ。米国のIntelは、14nm FinFET CMOS技術によるオンチップキャッシュ用SRAM技術を発表する(講演番号17.1)。記憶容量は84Mビット。メモリセル面積は0.0500μm2と極めて小さい。動作周波数は1.5GHzである。米国のIBMは、14nm技術によるオンチップキャッシュ用DRAM技術を報告する(講演番号17.4)。ランダムアクセス時間は1.0nsと極めて短い。

関連記事

NANDフラッシュの基本動作(前編)

NANDフラッシュの基本動作(前編)

SSDを知るには、その記憶媒体として採用されているNANDフラッシュメモリを理解することも重要だ。今回は、NANDフラッシュメモリの基本動作を詳しく説明する。 19nm第2世代NAND搭載、2.5型SSHD

19nm第2世代NAND搭載、2.5型SSHD

東芝は、2.5型のソリッドステートハイブリッドドライブ(SSHD)として、「MQ02ABD100H」と「MQ02ABF050H」を商品化した。19nm第2世代プロセスのMLC型NANDフラッシュメモリを搭載している。 東芝がSKハイニックスと和解し、協業関係も強化

東芝がSKハイニックスと和解し、協業関係も強化

東芝は、NAND型フラッシュメモリの技術漏えいで、SKハイニックス(SK Hynix)を相手取り民事訴訟を起こしていた件について、両社が和解に至ったと発表した。 次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

次世代不揮発性メモリ市場が成長、MRAMとPCMは2016年に10億ドル規模へ

NAND型フラッシュメモリの微細化と大容量化は限界に近づいている。メモリセルを垂直に積み上げる3次元構造のNANDフラッシュの開発も進んでいるが、MRAMやPCMといった次世代不揮発性メモリが、NANDフラッシュに代わって大きく伸びることが予測されている。 用途に合わせた選択を――SSDの正しい知識

用途に合わせた選択を――SSDの正しい知識

最近になり、価格がぐっと下がってきたSSD。PC購入時の選択肢に、内蔵ストレージをHDDとSSDのどちらかから選べるケースも増えてきました。“HDDの高性能版”のような印象を受けるSSDですが、その実態はどうなのでしょうか。今回は、SSDの基本的な仕組みやHDDとの比較、PC以外でのSSDの適応分野を紹介します。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR