EE Times Japan >

プロセス技術 >

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(ASML編):福田昭のデバイス通信(88)(2/2 ページ)

» 2016年09月14日 10時30分 公開

[福田昭,EE Times Japan]

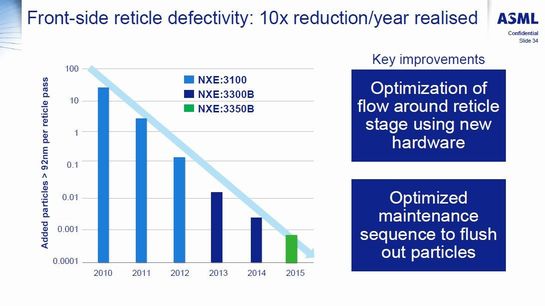

急速に下がってきたマスクの欠陥密度

EUVリソグラフィが抱える大きな課題に、マスク(レチクル)の欠陥がある。これについてLercel氏はかなり積極的な見解を示していた。過去6年ほど、「1年で10分の1」という速いペースで欠陥密度は低下してきた。2010年の欠陥密度に対して2015年の欠陥密度はおよそ1万分の1に下がっている。このペースが今後も続くのであれば、未来は明るい。

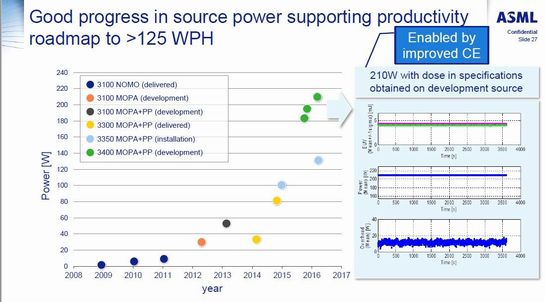

最大の課題「光源の出力」がついに向上してきた

そしてもう1つの重要な課題で、最大の課題とされてきた光源の出力が、ついに上昇してきた。最近まで光源の出力は思うように上がらず、このためにスループットが実用的な要求仕様よりもはるかに低いままにとどまっていた。

それが現在では3年前の2倍以上、125Wを実現できている。125Wの光源による露光装置のスループットは300mmウエハーで1時間当たり85枚を達成しており、目標である125枚/時間にぐっと近づいた。開発段階の光源出力は200Wに達しており、ASLMは次期のEUV露光装置に、この高出力光源を搭載する予定である。最大出力では210Wに到達するもようだ。

2018年〜2019年には7nm世代のロジック半導体の量産が始まるとASMLは想定している。7nmロジックは、ArF液浸とEUVの組み合わせ(いわゆる「ミックス・アンド・マッチ」)で乗り切る構えだ。

(次回に続く)

関連記事

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(東京エレクトロン編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(東京エレクトロン編)

今回は、7nm世代以降の半導体製造プロセスで使わざるを得なくなるだろう「自己整合(セルフアライン)的なリソグラフィ技術」に触れる。その候補は3つ。東京エレクトロンのBen Rathsack氏が、3つの候補技術の現状を紹介した。 「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(ニコン編)

「SEMICON West 2016」、7nm世代以降のリソグラフィ技術(ニコン編)

90nm世代から商業化が始まったArF液浸スキャナーだが、3xnm世代に入ると、解像力は限界に達する。そこで、コスト増というデメリットは伴うものの、マルチパターニングによって解像力の向上が図られてきた。加えて、7nm世代向けのArF液浸スキャナーでは新しいリソグラフィ技術の導入も必要だとされている。この場合、コスト面ではダブルパターニングと電子ビーム直接描画の組み合わせが有利なようだ。 ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。 着実に進歩するEUV、課題は光源

着実に進歩するEUV、課題は光源

EUV(極端紫外線)リソグラフィ技術は、着実に進化を遂げている。業界には、2018年ごろの実用化を望む声も多いが、当面の課題は光源の強さをどう向上するかにありそうだ。 ASMLがEUV装置を15台受注、納品先はIntel?

ASMLがEUV装置を15台受注、納品先はIntel?

ASMLが、EUV(極端紫外線)リソグラフィ装置を15台、“米国顧客企業の1社”に納入すると発表し、業界の観測筋の間でさまざまな臆測を呼んでいる。複数の情報筋が、この顧客企業がIntelではないかという見方を示している。 IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- キオクシアが超高IOPS SSD開発 NVIDIA Storage-Nextに対応

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

Special SitePR

あなたにおすすめの記事PR