imecが研究中のシリコンフォトニクス・プラットフォーム:福田昭のデバイス通信(146) imecが語る最新のシリコンフォトニクス技術(6)(2/2 ページ)

» 2018年05月11日 10時30分 公開

[福田昭,EE Times Japan]

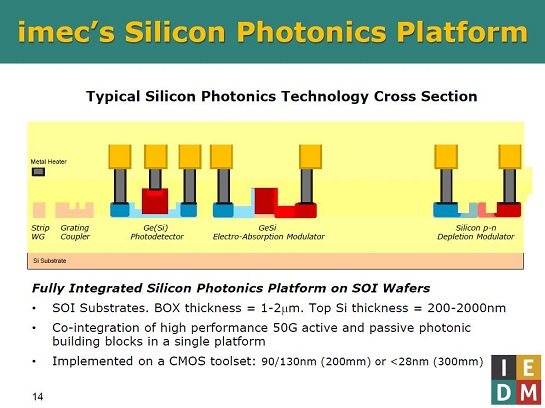

SOIウエハーのシリコン層に各種の光回路を作り込む

シリコンフォトニクスが使うウエハーはバルクではなく、二酸化シリコン層を埋め込んだSOI(Silicon On Insulator)ウエハーである。CMOSロジックの高速デジタル回路と、フォトニクスに特有の光回路をシリコン層に作り込む。シリコンの光導波路、シリコンの回折格子型光ファイバー結合器、Ge(あるいはSi)の光検出器、GeSiの電界吸収型変調器、シリコンのpn接合によるキャリア空乏型変調器、金属配線層によるヒーター(加熱回路)などである。

直径が200mmのシリコンウエハーを扱うシリコンフォトニクスのCMOSロジックは90nm/130nmの製造技術、直径が300mmと大きなシリコンウエハーを扱うシリコンフォトニクスのCMOSロジックは28nm以下の製造技術を使う。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

光送受信モジュールの技術開発ロードマップ

光送受信モジュールの技術開発ロードマップ

今回は、実装技術と光送受信モジュール技術のロードマップを解説する。光送受信モジュールの高速化と広帯域化では、波長分割多重(WDM)技術が重要になってくる。 シリコンフォトニクスとは何か

シリコンフォトニクスとは何か

今回は、「シリコンフォトニクス」技術を紹介する。そもそも「シリコンフォトニクス」とは何か、そしてその利点と課題について解説したい。 NVIDIAが解説するディープラーニングの基礎(前編)

NVIDIAが解説するディープラーニングの基礎(前編)

エヌビディアは2018年4月24日、ディープラーニングに関するセミナー「NVIDIA Deep Learning Seminar 2018」を東京都内で開催した。本稿では、セッション「これから始める人のためのディープラーニング基礎講座」から、ディープラーニングの歴史や概要、学習の流れについて紹介する。 記憶容量と書き換え回数から最適な埋め込みメモリを選択

記憶容量と書き換え回数から最適な埋め込みメモリを選択

半導体デバイス技術に関する国際会議「IEDM」で行われたセミナー「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」の概要を今回からシリーズで紹介する。 モバイル端末向けの最先端パッケージング技術

モバイル端末向けの最先端パッケージング技術

今回から、モバイル端末向けのパッケージング技術について解説する。大きく分けて、ウエハーレベルのファンアウトパッケージング(FOWLP)、パネルレベルのファンアウトパッケージング(FOPLP)、プリント基板へ回路素子を埋め込むパッケージング(ESP)がある。まずは、パッケージング技術における「ファンアウト」の意味を確認しつつ、Infineon Technologiesが開発した“元祖FOWLP”を説明したい。 シリコンインターポーザを導入した高性能パッケージの製品例

シリコンインターポーザを導入した高性能パッケージの製品例

シリコンインターポーザを導入したパッケージの製品化時期は、おおむね、2012年の第1期と、2015〜2016年の第2期に分けられる。それぞれの時期を代表する製品例と、それらの特徴を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR