「当面は微細化を進められる」 TSMCが強調:5nm、3nmへと突き進む(2/2 ページ)

2019年第3四半期に控えるEUV導入

TSMCは、2019年第3四半期に量産開始を予定している7+(N7+)nmプロセスにおいて、重要なレイヤーのいくつかに、同社初となるEUV(極端紫外線)プロセスを導入するという。N6では、EUVを適用するレイヤーをもう一つ増やし、N5ではさらにそれを増やしたとする。EUVの導入により、N7+ではマスク数が10%減少するという。N6とN5ではさらに少なくできる見込みで、それは注目に値するだろう。

最新のEUV装置の光源は、280Wを安定して出力できるという。TSMCは、光源の出力が2019年末には300Wに、2020年には350Wに達すると見込んでいる。アップタイムは2018年の70%から、現在では85%に向上しているが、2020年には90%に達する予定だ。TSMCのMii氏は「EUVはわれわれのニーズを上回った」と述べた。

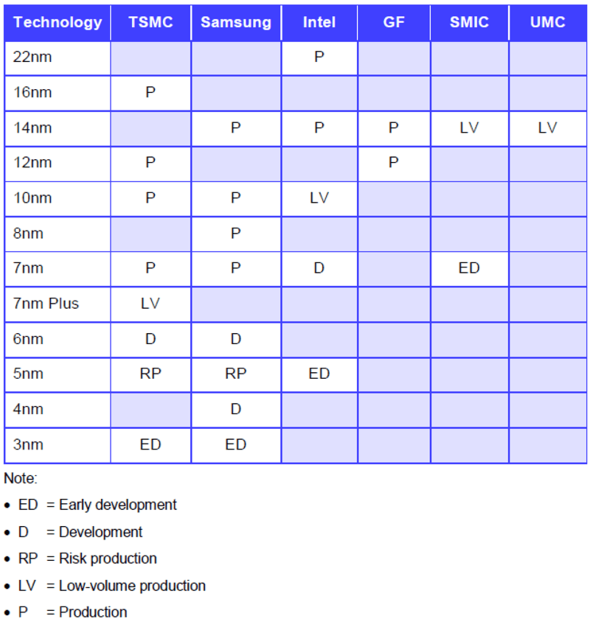

追加されたプロセスのオプションに、誰もが魅了されたわけではない。別のアナリストは、設計者らに対し、TSMCとSamsungからの暫定的なノードをスキップするよう助言した。IBS(International Business Strategies)のプレジデントであるHandel Jones氏は「顧客は5nmと3nmに焦点を当て、6nmや4nmといった他のオプションの一部は無視すべきだ」と述べた。

Jones氏は、ファウンドリーが新しいプロセスを適用した際は、初期の不良を避けるため、10万枚のウエハーを製造するまで待つように、とも助言した。

TSMCは、3nmおよび、2nmプロセスの研究開発を進めていると報告したが、今後必要となる新たなトランジスタについて説明するまでには至らなかった。Mii氏は、「硫化物とセレン化物の2D(2次元)素材を用いると、移動度の向上が期待できる。チャネルの厚さが1nm以下となり、7nmのゲート長のシリコンよりも高い駆動電流を供給できるからだ」と説明した。

22nmでは、0.6〜0.9Vをサポートへ

TSMCは、よりメインストリームのプロセスについて、「22ULL」プロセスは、バッテリー駆動のチップ向けに0.6〜0.9Vをサポートする予定だと述べた。HDMIブロックは現在開発中で、USB、MIPI、LPDDRブロックは、28nmプロセスのアップグレードプロセスに適しているかどうかを検証中だという。

パッケージングでは、TSMCは最新のオプションであるSoIC(System on Integrated Chip)とWafer-on-Wafer(WoW)の詳細を明らかにした。WoWは、同じサイズの2つのチップにのみ適用できるが、SoICは異なるサイズのダイを積層できるという。いずれも、モバイルならびに高性能のコンピュータシステムをターゲットにしているが、まだ開発段階にあり、商用化は2021年以降となる見込みだ。

【翻訳:青山麻由子、田中留美、編集:EE Times Japan】

関連記事

Samsungが5nmプロセスの開発を完了、2020年に量産

Samsungが5nmプロセスの開発を完了、2020年に量産

Samsung Electronics(以下、Samsung)は、EUV(極端紫外線)を用いた5nmプロセスの開発が完了し、受注を開始したと発表した。 3nm止まりか1nmか、微細化はレジスト開発が鍵

3nm止まりか1nmか、微細化はレジスト開発が鍵

半導体リソグラフィ技術に関する国際会議「SPIE Advanced Lithography 2019」で行われたパネルセッションの中で、エンジニアたちは、「半導体ロードマップはこの先、10年間延長して1nmプロセスまで実現できる可能性もあれば、新しいレジスト材の不足によって、3nmプロセスで行き詰まる可能性もある」と、希望や不安について語った。 10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか

Intelは2016年以降、今日に至るまで、10nmプロセスを立ち上げることができていない。一方で、配線ピッチは同等であるはずの、TSMCとSamsung Electronicsの7nmプロセスは計画通りに進んでいる。ではなぜ、Intelは10nmプロセスの立ち上げに苦戦しているのだろうか。 Samsung、EUV適用7nmチップ開発を加速

Samsung、EUV適用7nmチップ開発を加速

ファウンドリーの間で現在、EUV(極端紫外線)リソグラフィを使用した業界初となる半導体チップを実現すべく、競争が繰り広げられている。Samsung Electronics(以下、Samsung)は、「EUVリソグラフィを適用した複数の7nmプロセスチップをテープアウトした」と発表した。 ASML、EUVシステムを2019年に30台出荷する見通し

ASML、EUVシステムを2019年に30台出荷する見通し

ASMLが2018年7月18日(オランダ時間)に発表したところによると、同社は2018年に20台のEUV(極端紫外線)露光システムを、2019年には少なくとも30台を出荷する予定だという。 Samsung、19年Q1の業績は大幅悪化 メモリ不況で

Samsung、19年Q1の業績は大幅悪化 メモリ不況で

Samsung Electronics(以下、Samsung)は、DRAMおよびNAND型フラッシュメモリチップの価格が継続的に下落する中、2019年第1四半期の売上高、利益とも大幅に減少する見込みだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待