3次元積層モジュール「SoIC」の高性能化を支援する高放熱技術:福田昭のデバイス通信(340) TSMCが開発してきた最先端パッケージング技術(13)(2/2 ページ)

積層するダイの枚数増で発熱が急速に増大

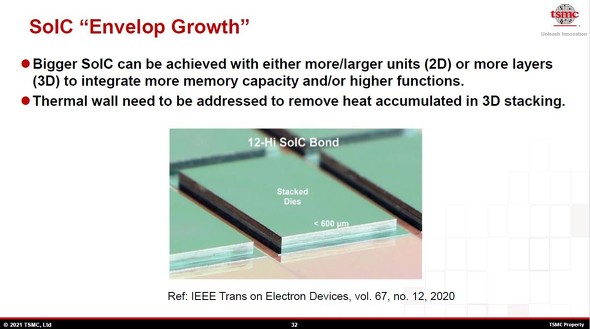

TSMCが気にかけているのが、シリコンダイを3次元積層する「SoIC(System on Integrated Chips)」技術のスケーリングだ。SoICでは、積層するシリコンダイの枚数を増やすことでスケールアップを図る。複数のモジュールを収容するパッケージ全体では、SoICモジュールの消費電力密度が突出して高くなってしまう恐れが少なくない。

12枚のシリコンダイをSoIC技術で積層したモジュールの外観[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

12枚のシリコンダイをSoIC技術で積層したモジュールの外観[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)そこで開発を進めているのが、従来の「伝導水冷」を超える性能の水冷技術である。通常の伝導水冷では、冷却水が通過するパイプラインを内蔵したヒートシンクと、シリコンダイあるいはパッケージを熱的に接続する。接続には熱抵抗の低い材料(「TIM(Thermal Interface Material)」と呼ぶ)で構成したゲルやフィルムなどを使う。

TSMCが開発している水冷技術は、シリコンダイ(放熱用ダイ)でシリコンダイ(電子回路を作り込んだ通常のダイ)を冷却するというものだ。放熱用のシリコンダイは、表面に細長い柱(ピラー)のアレイ、あるいは溝(トレンチ)のアレイを形成してある。放熱用ダイの表面に水を通すことで、シリコンダイ(電子回路を作り込んだダイ)の発熱を逃がす。

放熱用シリコンダイによる水冷の概要。放熱用シリコンダイの表面に細長い柱(ピラー)のアレイ、あるいは溝(トレンチ)のアレイを形成し、冷却水を流す[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)

放熱用シリコンダイによる水冷の概要。放熱用シリコンダイの表面に細長い柱(ピラー)のアレイ、あるいは溝(トレンチ)のアレイを形成し、冷却水を流す[クリックで拡大] 出所:TSMC(2021 VLSI Technology Symposiumの講演「Ultra High Power Cooling Solution for 3D-ICs」(講演番号JFS1-4)のスライドから)ここで重要なのは、ピラーおよびトレンチの形成にエッチング技術ではなく、ダイシングソー技術を使うことだ。ダイヤモンドカッターによってウェハーに切り込みを入れることで、ピラーあるいはトレンチのアレイを作る。エッチング技術に比べると加工のコストが低い。

ピラーアレイあるいはトレンチアレイの幅は200μm、間隔は210μm、深さ(高さ)は400μmである。シリコンウェハーは直径が300mm、厚みが750μm。テスト用ダイ(TTV:Thermal Test Vehicle)と放熱用ダイ(Lid)はウェハーレベルでハイブリッド接合する。接合部のTIMはシリコン酸化膜である。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

ウエハースケールの超巨大プロセッサを実現した「InFO」技術

「InFO」技術を改良した2種類のパッケージのうち、ウエハー規模の巨大なパッケージング技術「InFO_SoW」を解説する。 モバイル向け小型薄型パッケージ「InFO」が進化

モバイル向け小型薄型パッケージ「InFO」が進化

TSMCが開発してきた先進パッケージング技術の最新動向を紹介する。始めは全体のトレンドを示す。 「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待