imecも全幅の信頼、Rapidusの「成功の定義」とは何か:湯之上隆のナノフォーカス(68)(7/7 ページ)

先端ロジック半導体のロードマップとASMLとの提携

半導体のロードマップとしては、かつて、ITRS(International Technology Roadmap for Semiconductors)があった。ところが、そのロードマップがシステムなどの動向を考慮しないと決められないようになったことから、2016年からはIRDS(International Roadmap for Devices and Systems)が公開されるようになった。

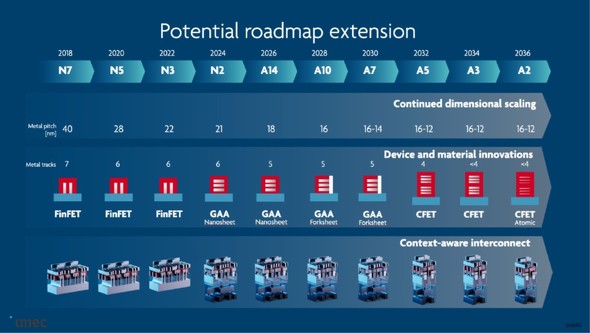

しかし筆者は、あるときから国際学会でのimecの発表の方が、半導体の将来像を正しく示しているように思い始めた。そのimecは、今回のITFで、先端ロジック半導体のロードマップとして、図11を示している。

現在、TSMCとSamsungが3nmの量産を行っている。そして、imecのロードマップによれば、2024年にGAA(Gate All Around)構造のN2が量産されることになっているが、ちょっとこれは早すぎで、恐らく2025〜2026年にずれ込むと踏んでいる。

このように、実際の量産とは時期がずれる可能性があるが、トランジスタの構造や微細配線のピッチなどは、imecのロードマップが半導体業界の道しるべになっていると思う。

そして、imecはオランダのASMLと提携して、先端リソグラフィ技術の開発を行っている。今回のITF Japanの第2部では、imecのSVP(Senior Vice President)でAdvanced Patterningを担当しているSteven Scheer氏が、EUV露光装置の次世代機、High NAのプロトタイプ1号機の評価が2024年前半に始まることを発表した(図12)。

これまでASMLは、2023年後半にHigh NAの評価を始めるとアナウンスしていたので、プロトタイプ1号機の製造などが若干遅延しているのかもしれない。

筆者プロフィール

湯之上隆(ゆのがみ たかし)微細加工研究所 所長

1961年生まれ。静岡県出身。京都大学大学院(原子核工学専攻)を修了後、日立製作所入社。以降16年に渡り、中央研究所、半導体事業部、エルピーダメモリ(出向)、半導体先端テクノロジーズ(出向)にて半導体の微細加工技術開発に従事。2000年に京都大学より工学博士取得。現在、微細加工研究所の所長として、半導体・電機産業関係企業のコンサルタントおよびジャーナリストの仕事に従事。著書に『日本「半導体」敗戦』(光文社)、『「電機・半導体」大崩壊の教訓』(日本文芸社)、『日本型モノづくりの敗北 零戦・半導体・テレビ』(文春新書)。2023年4月には『半導体有事』(文春新書)を上梓。

関連記事

史上最悪レベルの半導体不況に回復の兆し、生成AIという新たな“けん引役”も

史上最悪レベルの半導体不況に回復の兆し、生成AIという新たな“けん引役”も

“コロナ特需”から一転、かつてないレベルの不況に突入した半導体業界だが、どうやら回復の兆しが見えてきたようだ。本稿では、半導体市場の統計や、大手メーカーの決算報告を基に、半導体市場の回復時期を探る。さらに、業界の新たなけん引役となりそうな生成AIについても言及する。 裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023

裏面電源供給がブレークする予感、そしてDRAMも3次元化に加速 〜VLSI2023

2023年6月に開催された「VLSIシンポジウム2023」は大盛況であった。本稿では、筆者が“ブレークの予感”を抱いた裏面電源供給技術と、3D(3次元) NAND/DRAM技術に焦点を当てて、解説する。 日本の前工程装置のシェア低下が止まらない 〜一筋の光明はCanonの戦略

日本の前工程装置のシェア低下が止まらない 〜一筋の光明はCanonの戦略

筆者は2022年7月のコラムで、日本の前工程装置の世界シェアが、2010年から2021年にかけて急落していることを報告した。2022年もその状況は改善されていない。だが、露光装置には、一筋の光明を見いだせそうである。 投稿論文が激増した「VLSIシンポジウム2023」、シンガポール国立大が台頭

投稿論文が激増した「VLSIシンポジウム2023」、シンガポール国立大が台頭

2023年6月に京都で開催される「VLSIシンポジウム2023」。ようやく、本格的なリアル開催が戻ってくるようだ。本稿では、デバイス分野のTechnologyおよび、回路分野のCircuitsそれぞれについて、投稿/採択論文数の分析を行う。 ここが変だよ 日本の半導体製造装置23品目輸出規制

ここが変だよ 日本の半導体製造装置23品目輸出規制

2023年3月、経済産業省は、半導体製造装置など23品目を輸出管理の対象として追加する方針を固めた。だが、ここで対象とされている製造装置、よくよく分析してみると、非常に「チグハグ」なのである。何がどうおかしいのか。本稿で解説したい。 半導体の微細化は2035年まで続く 〜先端ロジックのトランジスタと配線の行方

半導体の微細化は2035年まで続く 〜先端ロジックのトランジスタと配線の行方

2022年6月に開催された「VLSIシンポジウム」の講演のうち、最先端ロジック半導体に焦点を当てて解説する。ASMLが2023年から本格的に開発を始める次世代EUV(極端紫外線)露光装置「High NA」が実用化されれば、半導体の微細化は2035年まで続くと見られる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 次世代パワー半導体 「期待の5材料」の現在地

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門