スパンションが読み取り速度最大333MB/sの高速インタフェース技術を発表:メモリ/ストレージ技術

スパンションは、読み取りスループットが最大333Mバイト/秒と、従来のクワッドSPI(Serial Peripheral Interface)に比べて5倍の速度を実現したインタフェース技術「Spansion HyperBus」を発表した。この技術を用いてNORフラッシュメモリ「Spansion HyperFlash」を製品化した。HyperFlashは当初、128M/256M/512Mビット品の3種類を用意する。

スパンションは2014年2月18日、読み取りスループットが最大333Mバイト/秒と、従来のクワッドSPI(Serial Peripheral Interface)に比べて5倍の速度を実現したインタフェース技術「Spansion HyperBus」(以下、HyperBus)を発表した。この技術を用いてNORフラッシュメモリ「Spansion HyperFlash」(以下、HyperFlash)を製品化した。HyperFlashは当初、128M/256M/512Mビット品の3種類を用意する。512Mビット品は2014年4月以降にサンプル出荷を始める計画だ。また、HyperBus技術は複数社と既にライセンス契約を結んでおり、フリースケールは同技術を用いた車載向けマイクロコントローラなどを製品化する予定である。

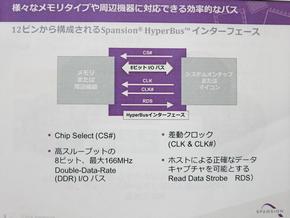

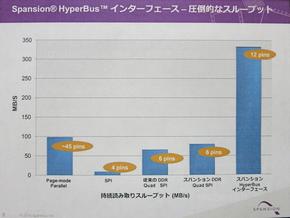

HyperBusインタフェースは、8本のアドレス/データバス、2本の作動クロック(CLK&CLK#)、チップセレクト(CS#)、および読み出し用ストローブ(RDS:Read Data Strobe)といった12本のバスで構成される。動作周波数は最大166MHzである。読み取りスループットは最大333Mバイト/秒を実現している。これは、パラレルインタフェースの90Mバイト/秒、同社のクワッドSPIの80Mバイト/秒(一般的な製品は40〜66Mバイト/秒)に比べて、極めて高速なデータ転送を可能とする。しかも、端子数はパラレルインタフェースに比べて1/3に削減することができる。

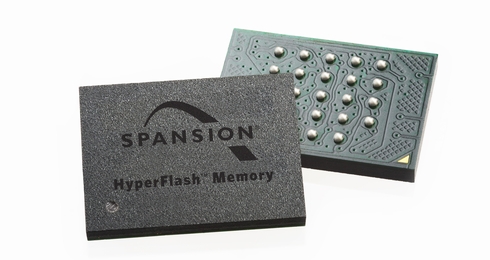

スパンションは、HyperBusインタフェース技術を用いたHyperFlashを同時に発表した。第1弾として製品化するのは、電源電圧が3.0V品と1.8V品の2タイプあり、メモリ容量は128Mビット品、256Mビット品、512Mビット品の3種類を用意する。読み取りスループットは1.8V品が333Mバイト/秒、3.0V品は200Mバイト/秒である。量産当初は65nmプロセスを用いて製造される。

パッケージは外形寸法が8×6mmの24端子BGAで供給する。端子配置は同社のクワッドSPI、デュアルクワッドSPI、およびHyperFlashと共通な配列とした。このため、ユーザーは基板の設計を変更することなく、シリーズ製品の中から用途に応じて性能とメモリ容量を選択することが可能だ。動作温度範囲は−40〜125℃と広く、車載用途にも対応できる仕様となっている。

スパンションでフラッシュメモリグループ NORプロダクトラインマネージメント担当のシニアディレクタを務める猪野浩永氏は、「HyperFlashは、車載向けクラスタやインフォテインメント機器、先進運転支援システム(ADAS)といった、インスタント・オンやインタラクティブなGUI機能が要求される車載用途などで高い可能性を秘めている」と話す。さらに、高速なメモリインタフェースを実現したことにより、ブートから画面表示までの時間を大幅に短縮することが可能となった。画像も低い圧縮率あるいは非圧縮のままで高速に転送でき、高品質の画像を確保することができるという。

- Type-C対応デュアルUSBメモリ、サンディスクが7月から出荷開始

- HyperBus対応「HyperRAM」、ボード設計を簡素化しシステム性能を向上

- 「経験で設計すると失敗する」、ルネサスが提示する16nm FinFET SRAMの課題

- NANDフラッシュ、売価下落も市場規模は拡大――2014年10〜12月

- 平均レスポンスタイム1ms以下、ネットアップのオールフラッシュアレイ

- 磁気メモリの新材料が登場か――ビスマスフェライトで新方向の電気分極を発見

- 高速書き込み/読み出しと優れた耐久性を実現、UHS-I U3対応microSDカード

- 16×20mmサイズ、256GB容量のPCIe対応SSD

- スパンションがMLC NANDメモリに参入――eMMCを製品化

- BDで1ラック当たり1ペタバイトを実現、HLDSの光ディスクライブラリ

関連記事

スパンションが車載用半導体の新製品投入を加速――今春にはCPU強化した新車載マイコンを出荷へ

スパンションが車載用半導体の新製品投入を加速――今春にはCPU強化した新車載マイコンを出荷へ

スパンションは、マイコン、アナログ半導体、フラッシュメモリという3つの主力製品分野ともに、自動車向け製品の強化を進めている。2014年1月15〜17日開催の「国際カーエレクトロニクス技術展」(東京ビッグサイト)でも、製品化前の参考出品も含めで各主力製品分野で新製品の提案を行った。 スパンション、2015年に40nm世代マイコン投入へ――マイコン事業強化方針を説明

スパンション、2015年に40nm世代マイコン投入へ――マイコン事業強化方針を説明

スパンションは2013年11月18日、都内で会見を開き、2013年8月に富士通から買収したマイコン/アナログ事業に関する事業方針の説明を行い、2015年に40nmプロセスを用いたフラッシュメモリ内蔵マイコンを投入する計画などを明かした。 Spansionが組み込み向けフラッシュ事業を加速、2年間で顧客数を倍増へ

Spansionが組み込み向けフラッシュ事業を加速、2年間で顧客数を倍増へ

NOR型フラッシュメモリ大手のSpansion(スパンション)は、3年ほど前から組み込み機器の市場にフォーカスした事業を展開してきた。高い信頼性と堅牢性を実現したフラッシュメモリ製品と技術サポート力で、さらなる顧客数の拡大を狙う。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

HyperFlashの外観

HyperFlashの外観 スパンションのシニアディレクタを務める猪野浩永氏

スパンションのシニアディレクタを務める猪野浩永氏