儉乕傾偺朄懃丄50擭傪偨偳傞丗敿摫懱媄弍 恑壔偺尮乮2/2 儁乕僕乯

儉乕傾偺朄懃巟偊偨僉乕僥僋僲儘僕乕

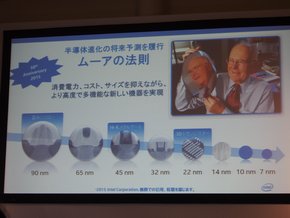

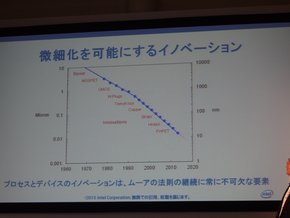

丂弴挷偵旝嵶壔偑恑傫偱偄偨僩儔儞僕僗僞傕丄2000擭偛傠丄120nm/130nm僾儘僙僗晅嬤傪嫬偵丄扨偵僾儘僙僗儖乕儖傪旝嵶壔偡傞偩偗偱偼惈擻偺岦忋偑恾傟側偔側偭偰偄偭偨丅惈擻傪岦忋偝偣偮偮丄掅徚旓揹椡壔傗掅僐僗僩壔傕幚尰偡傞偨傔偵丄Intel偼梫強梫強偱怴偟偄媄弍傪摫擖偟偰偒偨丅90nm僾儘僙僗偱偼榗傒僔儕僐儞傪嵦梡丄45nm僾儘僙僗偱偼僎乕僩巁壔枌傪崅桿揹棪/嬥懏僎乕僩乮HKMG丗High-k/Metal Gate乯偵抲偒姺偊丄22nm僾儘僙僗偱偼3師尦峔憿傪揔梡偟偨丅偙偆偟偨媄弍偑丄儉乕傾偺朄懃偵増偭偨旝嵶壔傪巟偊偰偒偨偺偱偁傞丅垻晹巵偼丄乽偮傑傝崱屻偺10nm丄7nm側偳偱傕丄壗偐偟傜偺怴偟偄媄弍傪摫擖偡傞偲偄偆偙偲偩乿偲榖偟偰偄傞丅

7nm丄5nm乧乧旝嵶壔偼懕偔傕壽戣偼嶳愊傒

丂壗搙傕乽尷奅愢乿偑彞偊傜傟偰偒偨儉乕傾偺朄懃偩偑丄僩儔儞僕僗僞偺旝嵶壔偼傑偩懕偄偰偄傞丅Intel偼尰嵼丄10nm僾儘僙僗傪奐敪拞偱丄7nm丄5nm偺尋媶偵傕庢傝慻傫偱偄傞丅偩偑丄垻晹巵偼乽壽戣偼嶳愊傒偩乿偲榖偡丅乽傑偢偼業岝憰抲偩丅EUV乮嬌抂巼奜慄乯業岝憰抲偺搊応傪丄Intel偵尷傜偢嬈奅慡懱偑懸偪朷傫偱偄傞丅EUV業岝媄弍乮偺奐敪乯偼丄擔杮偺懚嵼姶傕崅偄暘栰偩丅偨偩丄Intel偱偼丄7nm僾儘僙僗偵偮偄偰偼EUV傪巊傢側偔偰傕幚尰偱偒傞曽朄傪峫偊偰偄傞乿乮垻晹巵乯丅

丂傑偨丄CMOS僩儔儞僕僗僞偲偼堎側傞摦嶌尨棟傪梡偄傞乽Beyond CMOS乿傗丄3師尦僩儔儞僕僗僞丄怴偨側僷僢働乕僕儞僌媄弍傕丄10nm埲崀傪幚尰偡傞尞偵側傞偲偄偆丅摨巵偼丄乽Intel偩偗偱偼丄僼儘儞僩僄儞僪偱傕僶僢僋僄儞僪偱傕壗傕偱偒側偄忬懺偵側偭偰偄偰丄僷乕僩僫乕偲偺嫤嬈偑寚偐偣側偔側偭偰偄傞丅嫤嬈偡傞働乕僗偑丄愄偲偼寘堘偄偵憹偊偨乿偲弎傋偰偄傞丅垻晹巵偼丄乽10nm僾儘僙僗偵偮偄偰偼丄廬棃偺Intel偺儖乕儖偵廬偭偰幚尰偱偒傞偺偱偼側偄偐偲姶偠偰偄傞乿偲榖偟偨丅

丂側偍丄僀儞僥儖偼2015擭壞丄儉乕傾偺朄懃50廃擭偵崌傢偣丄僾儘僙僢僒偺媄弍側偳傪徯夘偡傞揥帵傪壢妛媄弍娰乮搶嫗搒愮戙揷嬫杒偺娵岞墍乯偱峴偆丅庒偄悽戙偵岦偗偰丄僐儞僺儏乕僞傊壢妛傊偺嫽枴姭婲傪慱偆丅

娭楢婰帠

乽儉乕傾偺朄懃偼娫傕側偔廔偊傫傪寎偊傞乿丄Broadcom偺CTO偑岅傞

乽儉乕傾偺朄懃偼娫傕側偔廔偊傫傪寎偊傞乿丄Broadcom偺CTO偑岅傞

Broadcom偺CTO乮嵟崅媄弍愑擟幰乯偑丄乽儉乕傾偺朄懃偼偁偲15擭傎偳偱廔偊傫傪寎偊傞丅敿摫懱僾儘僙僗偺旝嵶壔偼丄5nm埲崀偼傎傏恑曕偟側偄乿偲偄偆尒夝傪帵偟偨丅 儉乕傾偺朄懃偼5nm偵暻丄柉惗梡LSI偼28nm偱條巕尒傪

儉乕傾偺朄懃偼5nm偵暻丄柉惗梡LSI偼28nm偱條巕尒傪

儉乕傾偺朄懃偵偮偄偰偺尒夝傪悢懡偔弎傋偰偄傞Broadcom偺CTO丄Henry Samueli巵丅旝嵶壔媄弍偺崱屻傗丄IoT巗応偺摦岦丄摨幮偺儀乕僗僶儞僪帠嬈揚戅側偳偵偮偄偰丄榖傪暦偄偨丅 儉乕傾偺朄懃丄偦偺峴曽傪暦偔

儉乕傾偺朄懃丄偦偺峴曽傪暦偔

偙傟傑偱壗搙偲側偔乬廔偊傫愢乭偑彞偊傜傟偰偒偨儉乕傾偺朄懃偩偑丄敿摫懱嬈奅偼懡戝側楯椡偱偙偺朄懃傪堐帩偟偰偄傞丅崱屻丄儉乕傾偺朄懃偼偳偆側偭偰偄偔偺偐丅嬈奅偺僉乕儅儞偵丄儉乕傾偺朄懃偺峴曽傗丄儉乕傾偺朄懃偺堐帩偵娭傢傞媄弍側偳偵偮偄偰榖傪暦偄偨丅 SoC愝寁幰偑乬億僗僩丒儉乕傾偺朄懃帪戙乭傪惗偒敳偔弍

SoC愝寁幰偑乬億僗僩丒儉乕傾偺朄懃帪戙乭傪惗偒敳偔弍

僠僢僾愝寁幰偵乽僞僟斞乿傪偛偪偦偆偟偰偔傟偨乬儉乕傾偺朄懃乭偑側偔側傠偆偲偟偰偄傞丅偙傟偐傜僠僢僾愝寁幰偑惗偒偰偄偔偵偼惈擻岦忋偲徚旓揹椡掅尭傪幚尰偡傞妚怴揑曽朄傪帺傜惗傒弌偟偰偄偔偟偐側偄丅 廔偊傫娫嬤偺儉乕傾偺朄懃丄乬億僗僩CMOS乭偺媄弍傪柾嶕傊

廔偊傫娫嬤偺儉乕傾偺朄懃丄乬億僗僩CMOS乭偺媄弍傪柾嶕傊

暷崙偱奐嵜偝傟偨僔儞億僕僂儉乽IEEE Technology Time Machine乮TTM乯2014乿偱偼丄乬億僗僩CMOS乭偺媄弍偵偮偄偰媍榑偑岎傢偝傟偨丅拲栚偝傟偰偄傞偺偼丄検巕僐儞僺儏乕僞丄價僢僌僨乕僞丄僇乕儃儞僫僲僠儏乕僽丄恖娫偺擼乮僔僫僾僗乯傪傑偹偨媄弍側偳偱偁傞丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 乽Renesas 365乿偑偮偄偵巒摦 乽晄壜擻偩偭偨婯柾乿偺専徹丄悢暘偱

- NVIDIA偲儊儌儕3幮丄悽奅敿摫懱攧忋崅偺42亾愯傔傞

- 僀儔儞愴憟偺挿婜壔偑敿摫懱嬈奅偵媦傏偡怺崗側塭嬁

- 僨儞僜乕丄儘乕儉偵懳偡傞姅幃庢摼採埬傪惓幃昞柧

- 崅NA EUV傪乽嶻嬈婯柾傊奼挘乿丄imec偑EXE:5200摫擖

- Arm偑敿摫懱偺帺幮奐敪偵嶲擖丄AI僨乕僞僙儞僞乕岦偗CPU敪昞

- 搶幣偲偺嫤媍傗僨儞僜乕採埬傊偺懳墳丄儘乕儉偑怴惡柧

- 僉僆僋僔傾偑Nanya偵774壄墌弌帒丄DRAM挿婜嫙媼宊栺傪掲寢

- 僉僆僋僔傾偑挻崅IOPS SSD奐敪 NVIDIA Storage-Next偵懳墳

- AI偺嫞憟幉偼敿摫懱偐傜揹椡傊乗乗擔杮偺愴棯偺乽巰妏乿偵