Broadcom偑ARM儀乕僗偺64價僢僩SoC搳擖傊丄MIPS偐傜僔僼僩丗僾儘僙僢僒/儅僀僐儞乮2/2 儁乕僕乯

Freescale傕ARM儀乕僗偺捠怣岦偗僾儘僙僢僒傪敪昞

丂Freescale傕丄2012擭拞弡偵敪昞偟偨傾乕僉僥僋僠儍乽Layerscape乿傪嵦梡偟偨丄摨幮弶偲側傞ARM儀乕僗偺捠怣岦偗僾儘僙僢僒傪敪昞偡傞梊掕偩丅偙傟傑偱丄Freescale偼丄僴僀僄儞僪捠怣僾儘僙僢僒岦偗偵偼PowerPC僐傾傪撈帺偵愝寁偟偰偄偨丅

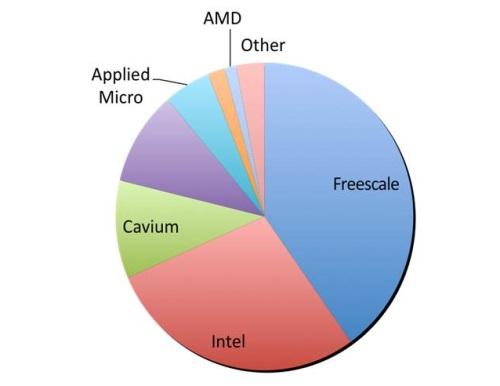

丂Gwennap巵偼丄乽偨偩偟丄Freescale偼丄2012擭偺捠怣僾儘僙僢僒巗応偺僔僃傾儔儞僉儞僌偱丄僔僃傾傪2億僀儞僩棊偲偟偰偄傞丅偦偺尨場偼丄柍慄婎抧嬊偺攧忋崅偺掅柪偵偁偭偨丅堦曽丄Broadcom偼NetLogic Microsystems偺攦廂偺寢壥丄崅偄怢傃傪婰榐偟偨丅Intel傕丄2012擭偼弴挷側惉挿傪悑偘偰偄傞乿偲夝愢偟偰偄傞丅摨巵偼傑偨丄乽捠怣僾儘僙僢僒偱偼丄Cavium偼屻傟傪庢偭偰偄傞丅摨幮偺捠怣僾儘僙僢僒亀Octeon II亁偼丄巗応搳擖偑抶偐偭偨乿偲捛壛偟偨丅

IP僐傾儀儞僟乕偺摦偒

丂Andes Technology偲ARM丄ASOCS丄Cadence Design Systems丄CEVA丄Imagination Technologies丄Synopsys偺7偮偺IP僐傾儀儞僟乕偼丄乽Linley Processor Conference乿乮2013擭10寧16乣17擔丄暷僇儕僼僅儖僯傾廈乯偱丄怴偟偄捠怣僐傾傗婛懚僐傾偺奼挘傪敪昞偟偨丅

丂CEVA偼丄戞4悽戙乽Ceva-XC乿僐傾傪敪昞偟偨丅廬棃偍傛傃師悽戙偺LTE僔僗僥儉偵岦偗傞丅摨幮偼丄乽戞4悽戙Ceva-XC偼丄柍慄僀儞僼儔岦偗偺弶偺晜摦彫悢揰DSP偩乿偲庡挘偟偰偄傞丅嵟戝40GFLOPS乮僊僈僼儘僢僾僗乯/W偺僄僱儖僊岠棪傪幚尰偟丄徚旓揹椡偼100mW偲彮側偄丅2亊2 MIMO傪嵦梡偟偨LTE岦偗僺僐僙儖偵懳墳偡傞偲偄偆丅

丂戜榩偵嫆揰傪抲偔Andes Technology偼丄乽N1337乿僐傾傪搳擖偟偰偄傞丅40LP乮Low Power乯僾儘僙僗傪揔梡偟丄1GHz傪忋夞傞崅偄廃攇悢偱摦嶌偡傞丅徚旓揹椡偼79mW/MHz偱丄1.88DMIPS/MHz丄2.41Coremark/MHz偺惈擻傪幚尰偡傞丅

丂Andes偼偙傟偲偼暿偵丄9000屄偺捛壛僎乕僩傪搵嵹偡傞僼儔僢僔儏儀乕僗偺儅僀僐儞偱丄徚旓揹椡偺掅尭偲惈擻偺岦忋傪恾傞孞傝曉偟僐乕僪僔乕働儞僗偺張棟媄弍乽FlashFetch乿媄弍傪敪昞偟偨丅儂僗僩CPU偺張棟懍搙偺1/4偱摦嶌偡傞僼儔僢僔儏儊儌儕偺応崌丄僼儔僢僔儏儊儌儕偺徚旓揹椡傪敿暘偵尭傜偟偰丄惈擻傪54乣120亾岦忋偱偒傞偲偄偆丅

丂ARM偼Linley Processor Conference偱丄乽Corelink乿僀儞僞乕僐僱僋僩偺奼挘斉傪敪昞偟偨丅ARM儀乕僗偺儅儖僠僐傾SoC偺惢憿偵岦偗傞丅Gwennap巵偼丄Linley Processor Conference偺婎挷島墘偱丄乽儊儌儕偺僶儞僪暆偲僺儞攝楍偼埶慠偲偟偰丄捠怣SoC偺庡梫側儃僩儖僱僢僋偵側偭偰偄傞乿偲弎傋偨丅

丂Gwennap巵偼丄EE Times偺儊乕儖庢嵽偺拞偱丄乽嵟戝偺懷堟暆偑昁梫側応崌丄傢傟傢傟偼僗僞僢僉儞僌偵傛偭偰懳張偟傛偆偲峫偊傞丅廬棃偺DDR愝寁傪傗傔偰丄怴偟偄崅懍僀儞僞僼僃乕僗偲慻傒崌傢偣傞応崌偼摿偵偦偆偩丅偟偐偟丄壙奿偺柺偐傜丄僐儌僨傿僥傿儊儌儕偑堷偒懕偒埑搢揑側僔僃傾傪愯傔傞偙偲偵側傞偩傠偆乿偲弎傋偰偄傞丅

亂東栿丗惵嶳杻桼巕丄戧杮杻婱丄曇廤丗EE Times Japan亃

- UI偺昞尰椡岦忋偱婡婍偺怴偨側壙抣傪憂憿丄儖僱僒僗偺HMI梡ASSP

- 儖僱僒僗丄壠揹/嶻婡偺晛媦儌僨儖偱僀儞僶乕僞惂屼傪幚尰偡傞FPU搵嵹掅壙奿儅僀僐儞

- RL78儅僀僐儞偑3攞懍偔側傞僐儞僷僀儔傪敪昞乗乗儖僱僒僗

- MSP430偺宯晥傪宲偖丄掅徚旓揹椡廳帇偺ARM Cortex-M4儅僀僐儞乽MSP432乿傪敪昞

- 僊僈價僢僩僀乕僒僱僢僩懳墳傪5僪儖埲壓偱幚尰丄16僐傾搵嵹儅僀僐儞

- 儖僱僒僗丄28nm悽戙崿嵹僼儔僢僔儏媄弍傪夵椙乗乗弴挷偵恑傓師悽戙幵嵹儅僀僐儞奐敪

- 乽Snapdragon乿偼偝傜偵崅惈擻偵丄64價僢僩Cortex-A72傪搵嵹

- 僌儔僼傿僢僋僗昞帵丄僎乕僕惂屼丄婡擻埨慡傪1僠僢僾偱幚尰丄儖僱僒僗偺32價僢僩儅僀僐儞

- 僌儔僼傿僢僋僗張棟偲儃僀僗惂屼偵懳墳丄HMI梡Cortex-M4搵嵹儅僀僐儞

- 儖僱僒僗丄2015擭搙撪偵SOTB嵦梡儅僀僐儞傪惢昳壔傊乗乗徚旓揹椡1/10埲壓丄0.4V嬱摦昳傕壜擻偵

娭楢僉乕儚乕僪

ARM | 捠怣 | Broadcom | 儀儞僟乕 | MIPS | 64價僢僩 | 僼儕乕僗働乕儖丒僙儈僐儞僟僋僞 | DSP乮Digital Signal Processor乯 | FinFET | PowerPC | 僒乕僶 | Imagination Technologies | ARM64 | 僾儘僙僢僒/儅僀僐儞乮僄儗僋僩儘僯僋僗乯

娭楢婰帠

Intel偑乬iPhone 5s偺A7乭偲摨偠64價僢僩SoC乽Quark乿傪敪昞乗乗儅僀僐儞巗応傪嫼偐偡偐丠

Intel偑乬iPhone 5s偺A7乭偲摨偠64價僢僩SoC乽Quark乿傪敪昞乗乗儅僀僐儞巗応傪嫼偐偡偐丠

Intel偼丄慻傒崬傒梡SoC乽Quark乿傪敪昞偟偨丅x86儀乕僗偺64價僢僩CPU傪桳偟丄廬棃偺慻傒崬傒梡SoC乽Atom乿偵斾傋偰丄僒僀僘偼5暘1丄徚旓揹椡偼10暘偺1偩偲偄偆丅64價僢僩偺傾僪儗僗嬻娫偺戝偒偝傪晲婍偵丄32價僢僩儅僀僐儞巗応傪嫼偐偡壜擻惈傕偁傞丅 乽1000壄墌偱傕摉幮偼攦偊側偄乿丄DSP僐傾偺CEVA偑帠嬈傪愢柧

乽1000壄墌偱傕摉幮偼攦偊側偄乿丄DSP僐傾偺CEVA偑帠嬈傪愢柧

僗儅乕僩僼僅儞傗僞僽儗僢僩抂枛偺撪晹偱柍慄捠怣傗僆乕僨傿僆丄價僨僆偺張棟傪扴偆DSP僐傾偱崅偄巗応僔僃傾傪埇傞IP僐傾儀儞僟乕偺CEVA丅恖堳婯柾偼悽奅偱190柤丄攧忋崅偼6000枩暷僪儖嫮偩偑丄乽1000壄墌偁偭偰傕摉幮傪攦廂偡傞偙偲偼偱偒側偄乿偲庡挘偡傞丅 CPU僐傾嬈奅偵抧妅曄摦丄MIPS傪Imagination偑攦廂

CPU僐傾嬈奅偵抧妅曄摦丄MIPS傪Imagination偑攦廂

儌僶僀儖岦偗僌儔僼傿僢僋僗僐傾偺Imagination Technologies偑丄CPU僐傾偺MIPS Technologies傪攦廂偡傞丅攦廂嬥妟偼6000枩暷僪儖丅偦傟偲暿偵MIPS偼丄強桳摿嫋偺8妱挻傪丄摿嫋曐帩婇嬈傪儊儞僶乕偲偡傞嬈奅僐儞僜乕僔傾儉偵3壄5000枩暷僪儖偱攧媝偡傞偲偄偆丅

Copyright © ITmedia, Inc. All Rights Reserved.

婰帠儔儞僉儞僌

- 僫僼僒婋婡偱敆傞乽儗僕僗僩嫙媼搑愨乿乗乗悽奅偺敿摫懱岺応傪掆巭偝偣傞丄傕偆堦偮偺椪奅揰

- TSMC偑師悽戙儘乕僪儅僢僾岞昞丂A13乛A12傪29擭搳擖傊

- 擖妛偟偨弖娫廔傢偭偨傢乗乗乽島媊偑塸岅乿側傫偰堦尵傕暦偄偰側偄両

- 嵟怴僲乕僩PC5婡庬傪暘夝丂怴媽MacBook Pro偺拞恎偺堘偄偼丠

- 乽憰抲偼摦偔偑僾儘僙僗偑惉棫偟側偄乿乗乗He嫙媼婋婡偲僫僼僒晄懌偺杮幙

- He乛僫僼僒嫙媼婋婡偱岺応怴愝傕抶墑丠 憰抲乛僠僢僾儊乕僇乕傊偺攇媦宱楬傪扵傞

- 乽悽奅弶乿惉壥偱1000憌挻3D僼儔僢僔儏偵摴嬝丄僉僆僋僔傾偲Sandisk

- Apple怴CEO偼僄儞僕僯傾弌恎丂惢昳奐敪廳帇傊偺夞婣偐

- 儘乕儉丒搶幣丒嶰旽揹婡偺僷儚乕敿摫懱偼偳偆側傞偐

- 師悽戙僷儚乕敿摫懱丂乽婜懸偺5嵽椏乿偺尰嵼抧

捠怣岦偗SoC偺僔僃傾丂Freescale偑儕乕僪偟偰偄傞偑丄僔僃傾偼尭彮偟偨丅堦曽丄Intel偲Broadcom偼僔僃傾傪奼戝偟偰偄傞乮僋儕僢僋偱奼戝乯丂弌揟丗The Linley Group

捠怣岦偗SoC偺僔僃傾丂Freescale偑儕乕僪偟偰偄傞偑丄僔僃傾偼尭彮偟偨丅堦曽丄Intel偲Broadcom偼僔僃傾傪奼戝偟偰偄傞乮僋儕僢僋偱奼戝乯丂弌揟丗The Linley Group