EE Times Japan『プログラマブルロジック』

「EE Times Japan『プログラマブルロジック』」の連載記事一覧です。

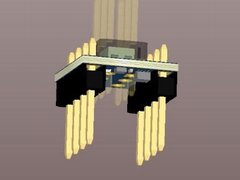

どう使う?:

ドイツのTrenz Electronicが、10mm×10mmのFPGAモジュールを5ドルで販売するプロジェクト「DIPSY」を進めている。2.54mmピッチのDILを採用し、5本のI/O端子はDIP8 PCB、ATtiny85と互換性のあるピン配置になっている。

普及は進む?:

EDA業界がIoT機器設計の分野に狙いを定めている。ASICを使ってIoT機器を設計することのメリットを強調し、クラウドを使った設計環境の提供に力を入れ始めている。

FPGA:

アルテラは、ハイエンドのプログラマブルロジックデバイス「Stratix10FPGA&SoC」のアーキテクチャと製品概要を発表した。新製品は「HyperFlexアーキテクチャ」や「ヘテロジニアス3D SiP(System in Package)インテグレーション」技術を採用している。製造はIntelの14nmトライゲートプロセスを用いて行われる。

プログラマブルロジック FPGA:

ザイリンクスは、All Programmable SoCおよびMPSoC向けの開発環境「SDSoC」を発表した。SDSoCを用いると、FPGAを設計した経験がほとんどない技術者でも、高速化したいC/C++関数を指定するだけで、自動的にハードウェア回路に置き換えることができる。

プログラマブルロジック FPGA:

アルテラは、20nmプロセス技術を用いて製造する第2世代SoC(System on Chip) FPGA「Arria 10 SoC」の出荷を開始した。前世代製品に比べて、処理性能を最大50%向上し、消費電力は最大40%削減できるという。

プログラマブルロジック FPGA:

ザイリンクスは、16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリを発表した。従来の28nmプロセスFPGA/SoCに比べて、消費電力当たり2〜5倍のシステム性能を実現することが可能となる。

プログラマブルロジック FPGA:

日本アルテラとマクニカは、アルテラ製「MAX 10 FPGA」を搭載した開発キットをそれぞれ発売する。MAX 10 FPGAを応用した産業機器や車載機器、IoT機器などのシステム開発を迅速に行うことが可能となる。

プログラマブルロジック:

ラティスセミコンダクターは2015年2月、ウェアラブル機器など向けに低消費電力化、小型化を追求した新しいFPGA「iCE40 UltraLiteファミリ」を発表した。

FPGA:

ザイリンクスは2014年12月、20nmプロセスを使用したFPGA「Kintex UltraScale KU040」の量産を開始したと発表した。

プログラマブルロジック:

Xilinx(ザイリンクス)は2014年11月、エンジニアリングサンプル(ES)出荷段階にある20nmプロセスを用いたFPGA「Virtex UltraScaleファミリ XCVU095」を使用した400Gビット イーサネットの動作デモを公開した。

プログラマブルロジック FPGA:

アルテラは、「Generation 10」製品群として、新たに「MAX 10 FPGA」を発表した。新製品は、2つのコンフィギュレーション用フラッシュメモリブロックやソフトコア「Nios II」プロセッサなどを搭載している。周辺機能を集積することで、同等性能のFPGAに比べて、ボード占有面積を最大50%も節減できるという。

プログラマブルロジック:

東芝は2014年6月、不揮発FPGAを実現可能なフラッシュメモリ混載技術を開発したと発表した。

これからのSDNは“Softly” Defined Network:

ザイリンクスは、SDN(Software-Defined Network)を構成するハードウェアを再構成可能なFPGAで実現する“Softly”Defined Networkを提唱している。しかし、これまでは“Softly”なSDNを構築するには大きな課題があったが、このほど「SDNet」と呼ぶ技術を開発し、FPGAによるSDNの実現に道を開いた。

HPC以外でもFPGAによるOpenCL利用が広がる:

アルテラは、並列コンピューティング向けソフトウェアプログラミングのフレームワークである「OpenCL(Open Computing Language)」への対応を積極的に行っている。2012年末には、並列コンピューティングの計算資源として手軽にFPGAが利用できるSDKの提供を開始し“OpenCL+FPGA”を実現。並列コンピューティング分野でのFPGAの普及状況やOpenCL対応を進める狙いなどについてアルテラの担当者に聞いた。

プログラマブルロジック FPGA:

アルテラは、同社製FPGAに内蔵するIEEE754準拠のハードウェア浮動小数点DSPを発表した。まず、20nmプロセスで製造される「Arria 10」FPGA&SoCと、14nmトライゲートプロセスで製造される「Stratix 10」FPGA&SoCで、ハードウェア浮動小数点DSPブロックを内蔵した製品を用意する。DSP性能はArria 10で最大1.5T FLOPS、Stratix 10で最大10T FLOPSを実現できるという。

プログラマブルロジック:

東京エレクトロン デバイスは、「Zynq-7000 All Programmable SoCセミナ2013」を開催した。会場内ではXilinx製ICチップ「Zynq-7000 All Programmable SoC」に関連した技術講演に加えて、パートナー企業がZynq-7000 All Programmable SoCを応用したハイビジョン映像の画像処理システムや開発支援ツールなどのデモ展示を行った。

プログラマブルロジック:

ザイリンクスは、20nmプロセス技術を用いたFPGAのテープアウト(設計完了)を発表した。同時に、20nmプロセス採用FPGAなどに適用する新世代アーキテクチャ「UltraScale」の概要も公表した。新プロセス、新アーキテクチャを採用した製品の出荷は2013年10〜12月を予定している。

プログラマブルロジック FPGA:

TabulaのFPGA「ABAX2P1 3PLD(Programmable Logic Device)」は、100ギガビット/秒(Gbps)クラスの信号を扱う通信機器などに向けたFPGAである。チップ上の2次元平面に「時間」の次元を加えた、独自の3次元PLD技術を採用しており、Intelの22nmプロセスで製造される。

プログラマブルロジック FPGA:

28nm世代の半導体プロセス技術で製造する最新FPGA「Xilinx 7シリーズ」のうち、既に量産出荷やサンプル出荷を始めていたハイエンド品「Virtex-7」とミドルレンジ品「Kintex-7」に続いて、このほど低コストと低消費電力を特徴とする「Artix-7」のサンプル出荷を開始した。

プログラマブルロジック FPGA:

これまで個別のデバイスとして存在していたFPGAとASIC、ASSP、DSP、プロセッサなどのシリコンチップをアプリケーションの要件に応じて組み合わせ、3次元技術で単一のパッケージに統合する。Alteraはこれで、柔軟性と消費電力当たりの性能がともに高いコンピューティングデバイスの実現を目指す。

記事ランキング