FPGAにハードウェア浮動小数点DSP内蔵、電力効率でGPGPUの上を行く:プログラマブルロジック FPGA

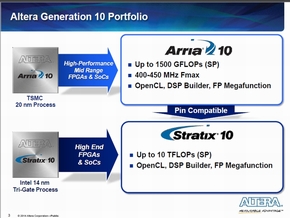

アルテラは、同社製FPGAに内蔵するIEEE754準拠のハードウェア浮動小数点DSPを発表した。まず、20nmプロセスで製造される「Arria 10」FPGA&SoCと、14nmトライゲートプロセスで製造される「Stratix 10」FPGA&SoCで、ハードウェア浮動小数点DSPブロックを内蔵した製品を用意する。DSP性能はArria 10で最大1.5T FLOPS、Stratix 10で最大10T FLOPSを実現できるという。

アルテラは2014年4月23日、同社製FPGAに内蔵するIEEE754準拠のハードウェア浮動小数点DSPを発表した。まず、20nmプロセスで製造される「Arria 10」FPGA&SoCと、14nmトライゲートプロセスで製造される「Stratix 10」FPGA&SoCで、ハードウェア浮動小数点DSPブロックを内蔵した製品を用意する。浮動小数点DSPブロックをハードウェア化したことで、DSP性能はArria 10で最大1.5T FLOPS、Stratix 10で最大10T FLOPSを実現できるという。

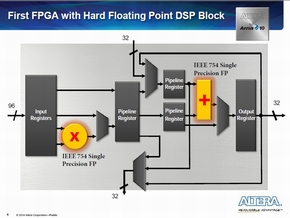

FPGAに内蔵するための、ハードウェア化された単精度浮動小数点DSPブロックは、同社の「可変精度DSPブロックアーキテクチャ」を活用している。これまでは、固定小数点マルチプライヤとFPGAロジックを利用して浮動小数点DSPブロックをFPGAに実装していた。今回開発したハードウェア浮動小数点DSPブロックを用いると、これまで必要だった1000以上のロジックエレメント(LE)をほとんど使わずに済む。このため、LEのリソースをそれ以外の回路ブロックに有効活用することが可能となる。

LEを使わないことでDSP性能も向上した。DSPブロックの動作周波数は、これまで最大200〜250MHzにとどまっていたのに対して、浮動小数点DSPブロック部分のLEを取り除いたArria 10では、最大400〜450MHzの動作周波数を可能とした。これにより、DSP性能は最大1.5T FLOPSを実現している。また、Arria 10に比べて動作周波数が2倍で、ロジックやDSP、メモリなどの密度が高いStratix 10では、10T FLOPSのDSP性能が得られるという。なお、浮動小数点または固定小数点のいずれのモードにするかは、DSP設計者が選択できる。

IEEE754準拠のハードウェア浮動小数点DSPを内蔵する20nm「Arria 10」と14nm「Stratix 10」の概要(左)、右はハードウェア浮動小数点DSPのブロック図 (クリックで拡大) 出典:アルテラ

IEEE754準拠のハードウェア浮動小数点DSPを内蔵する20nm「Arria 10」と14nm「Stratix 10」の概要(左)、右はハードウェア浮動小数点DSPのブロック図 (クリックで拡大) 出典:アルテラ浮動小数点DSPブロックをハードウェア化したことで、FPGAの設計期間も従来に比べて6〜12カ月間短縮することが可能となった。設計したDSPを、これまでのように固定小数点DSPブロックに置き換えることなく、ハードウェアの浮動小数点DSPブロックに直接書き換えることができるため、タイミング収束や検証に費やしていた時間を大幅に短縮することができるからだ。

ソフトウェア浮動小数点DSPブロックを実装した現行のArria 10から、ハードウェア浮動小数点DSPブロックを内蔵したArria 10に移行するための設計ツールとして、「OpenCL」や「DSP Builder」などを2014年下半期より提供していく。設計データを再コンパイルするだけで、容易に移行できるという。さらに、2015年にはStratix 10へ移行するための設計ツールも提供していく予定だ。なお、ハードウェア浮動小数点DSPブロックを内蔵したArria 10 FPGAはすでに出荷中である。

DSP性能を大幅に向上したことで、軍事用のレーダー用途やクラウドシステムにおけるビッグデータ解析、医療機器の画像処理、石油/ガス業界向けの地盤モデリングなどの用途でニーズが高まっているという。特に、ハードウェア浮動小数点DSPブロックをFPGAに内蔵したことで、「GPGPUや汎用DSPチップに比べて、電力消費や処理能力の点でFPGAがより優れたソリューションとなる」(同社)と話す。

関連キーワード

DSP(Digital Signal Processor) | FPGA関連 | FPGA | アルテラ | ハードウェア | 14nmプロセス | 20nmプロセス | 自動車 | GPGPU | GPUコンピューティング | OpenCL | ソフトウェア | 事業戦略 | プログラマブルロジック(エレクトロニクス) | プロセス技術(エレクトロニクス) | 電力効率 | フラッシュメモリ | 画像処理 | 日本法人 | 新製品

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ダメ半導体ベンチャーだったLattice SemiconductorのV字復活劇はPLDとともに

- Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

- 独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

- 飛躍するXilinx、AMDとの因縁も既に始まっていた!?

- FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

- レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

- Alteraの創業によるCPLDの萌芽でプログラマブルロジックはさらなる進化へ

- プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

- プログラマブルロジックの誕生――CPLD前史

関連記事

「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

アルテラは、「今すぐ使えるFPGAソリューション」をテーマに、最新のアルテラSoCやFPGAおよび評価ボードを展示した。パートナー製品も含めて、安価な評価キットやOpenCLを用いて設計が可能なFPGAアクセラレータボード、アルテラSoCを活用した自動車の運転支援システムなどのデモ展示が来場者の注目を集めていた。 全ての機器にアルテラ製品を、多様な製品群で自動車/産業機器分野に挑む

全ての機器にアルテラ製品を、多様な製品群で自動車/産業機器分野に挑む

大手FPGAベンダーのアルテラは、2013年後半から2014年にかけ、さまざまな新製品投入を予定する。14nmという最先端プロセス採用品から55nmフラッシュメモリ内蔵の低コストファミリ、さらには電源ICをも手掛ける。取り扱い製品が多様化しつつある中、2013年7月に日本アルテラの社長に就任したハンス・チュアン氏は、「全ての製品にアルテラ製品を搭載する」という。チュアン氏に日本法人社長としての抱負や事業戦略を聞いた。 シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

シリコンコンバージェンスを可能とするアルテラSoC、開発環境も整う

FPGAベースの設計手法は、設計の柔軟性を確保しつつ最先端プロセス技術を活用できることから注目を集めている。こうした中で「シリコンコンバージェンス」を提唱しているアルテラは、最先端FPGA技術をベースとしたSoC設計を推進している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

IEEE754準拠のハードウェア浮動小数点DSPを内蔵した20nm「Arria 10」の外観

IEEE754準拠のハードウェア浮動小数点DSPを内蔵した20nm「Arria 10」の外観