ARMの性能を超えるか、MIPSが新Aptivプロセッサで全面対抗:プロセッサ/マイコン(3/3 ページ)

IPブロック全体とプロセッサコアをそれぞれ改善

proAptivの処理性能を従来の1074Kよりも大幅に高めるため、同社は、IPブロック全体の処理(図3)とプロセッサコアの内部処理をそれぞれ改善している。全体の処理では大きく3つの改善点がある。まず、分岐予測のインプリメンテーションを改善した。次にこれまで外付けだった二次キャッシュコントローラーをコヒーレンシーマネジャーに内蔵したことで性能を高める。3番目に入出力バスであるIOCU(I/O Coherence Unit)を従来の1個から2個に増やした。つまりメインメモリ用のバスと合わせて3本のバス構成を採ることができる。

図3 proAptivの構成 同社が提供するIPの全体像「クラスタブロック」を示した。アウトオブオーダー・マルチイシューのコア(青)を1個から最大6個入る。その他、コアごとの電源や動作周波数の管理(最上部)、2次キャシュの整合性を保つコヒーレンスマネジャー(黄緑)、入出力管理ユニット(薄青)などから構成されている。 (クリックで拡大)

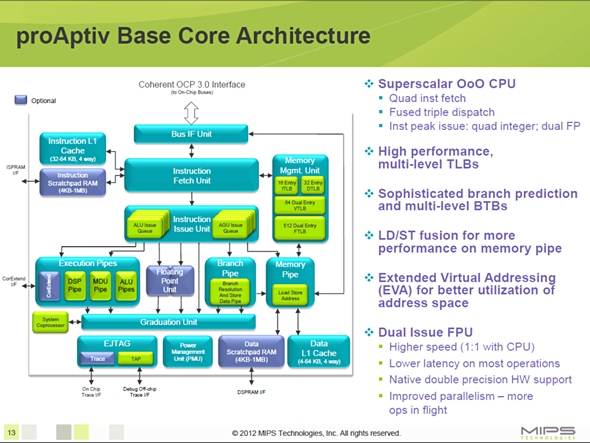

図3 proAptivの構成 同社が提供するIPの全体像「クラスタブロック」を示した。アウトオブオーダー・マルチイシューのコア(青)を1個から最大6個入る。その他、コアごとの電源や動作周波数の管理(最上部)、2次キャシュの整合性を保つコヒーレンスマネジャー(黄緑)、入出力管理ユニット(薄青)などから構成されている。 (クリックで拡大)次にプロセッサコアの内部処理を示す(図4)。プロセッサコア自体の処理能力は、4命令同時フェッチ(128ビット)、3命令同時ディスパッチ、4つの整数演算と2つの浮動小数点演算を同時実行できるように改良した。

浮動小数点処理ユニット(FPU)と遅延(レイテンシ)も改善した。従来の1074Kなどでは本体の約2分の1だった浮動小数点ユニットを本体と同じまで高め、レイテンシは従来の1074Kの半分に抑えた。

図4 proAptivのプロセッサコアの内部構成 図右上の「Memory Mgmt Unit」の改善がウェブ処理能力向上に直接寄与しているという。その下に描かれた「Memory Pipe」では1コア内の同一アドレスに対するリードライトを効率的に管理し、外部アクセスの頻度を低くするために役立つ。 (クリックで拡大)

図4 proAptivのプロセッサコアの内部構成 図右上の「Memory Mgmt Unit」の改善がウェブ処理能力向上に直接寄与しているという。その下に描かれた「Memory Pipe」では1コア内の同一アドレスに対するリードライトを効率的に管理し、外部アクセスの頻度を低くするために役立つ。 (クリックで拡大)proAptivの性能を引き出すには、ファウンドリに対して特別のプロセスを要求する必要がないという。例えばTSMCの標準的なプロセスを使うだけで、動作周波数1〜2GHzのプロセッサを製造できるとした。

なお、proAptivのユーザーメモリ空間は従来の最大2Gバイトから、3Gバイトへ拡張されている。ただし、アドレス空間の拡張手法はARMとは異なる。ARMのCortex-A15は従来の32ビット構成を物理的に40ビットに拡張して、メモリ空間を拡大した。proAptivでは物理的には32ビット構成のままTLB(Translation Look aside Buffer)内部に仮想アドレスビットを追加し、36ビットのアドレス空間を構成している。これをEVA(Extended Virtual Addressing)と呼ぶ。

- UIの表現力向上で機器の新たな価値を創造、ルネサスのHMI用ASSP

- ルネサス、家電/産機の普及モデルでインバータ制御を実現するFPU搭載低価格マイコン

- RL78マイコンが3倍速くなるコンパイラを発表――ルネサス

- MSP430の系譜を継ぐ、低消費電力重視のARM Cortex-M4マイコン「MSP432」を発表

- ギガビットイーサネット対応を5ドル以下で実現、16コア搭載マイコン

- ルネサス、28nm世代混載フラッシュ技術を改良――順調に進む次世代車載マイコン開発

- 「Snapdragon」はさらに高性能に、64ビットCortex-A72を搭載

- グラフィックス表示、ゲージ制御、機能安全を1チップで実現、ルネサスの32ビットマイコン

- グラフィックス処理とボイス制御に対応、HMI用Cortex-M4搭載マイコン

- ルネサス、2015年度内にSOTB採用マイコンを製品化へ――消費電力1/10以下、0.4V駆動品も可能に

関連記事

Googleが「MIPS版」Androidにてこ入れ

Googleが「MIPS版」Androidにてこ入れ

AndroidのNDK(Native Development Kit)へMIPS対応のGNUコンパイラなどを追加 Android 4.0搭載タブレット、ベースバンドチップにもMIPSアーキテクチャを採用

Android 4.0搭載タブレット、ベースバンドチップにもMIPSアーキテクチャを採用

Altair SemiconductorのMIPSベースのチップセット「FourGee LTE」を利用 プロセッサIPコアの実装手法

プロセッサIPコアの実装手法

MIPSコア「24Kc」に対する最適化の実例を紹介- MIPS、Androidアプリ開発ツールをリリース

プロセッサエミュレーションプラットフォーム「QEMU」やQEMU向けのJava開発ツール「Arriba」を利用

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増