ムーアの法則はまだ終わらない、存続の鍵はGaAs材料:プロセス技術(2/2 ページ)

理論上は4万2/V・sの電子移動度に?

POET TechnologiesでCTO(最高技術責任者)を務めるSimone氏は、EE Timesの取材に対し、「PETと呼ばれる当社のプラナー型エレクトロニクス技術は、集積可能な相補的インプレーン光学/電気デバイス技術を適用してCMOSを実現することで、n型MOS(NMOS)のような回路構造をベースにした従来のGaAs技術から大きく進歩した」と述べている。

POETのトランジスタチャネルはInGaAsで形成され、ガリウムをゼロに減らす(純粋なバルクInAsにする)ことで、理論的には4万2/V・sの電子移動度を実現できるという。ただし、POET Technologiesによると、ガリウムを可能な限りゼロに近づけてはいるが、ゼロにするのは不可能だという。同社は、「これまでのところ、インジウム53%のチャネルを実現した。最終的には、インジウムを80%にすることも可能だ」と述べている。

シリコンの1Xnm世代に匹敵

Taylor氏は、EE Timesに対して、「格子定数を特性に逆らった独自の編成方法で変更することで、こうした成果を達成した。GaAs基板上に、厚さ1μmのInGaAs歪み層を、InP(リン化インジウム)の格子定数に対応した自然量子井戸に達するまで何層も形成した。この時最も重要になるのが、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法によって薄膜結晶の構成を調整することだ」と語った。

POET Technologiesは、2014年後半に100nmプロセス技術を適用した試作品をサードパーティーのファウンドリで製造する計画だ。さらに、2015年までに40nmプロセス技術の適用を目指すという。シリコンでは既に20nmプロセスが採用され、Intelは14nmにまで微細化していることに比べると遅れているようにも思えるが、POET Technologiesは、「シリコンと比較することはフェアではない。POETにおける40nmプロセスは、シリコンの14〜10nmプロセスと比較すべきだ」と主張している。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連記事

LEDを一新した「GaN」、次は電力を変える

LEDを一新した「GaN」、次は電力を変える

SiC(炭化ケイ素)と並んで次世代パワー半導体の旗手として脚光を浴びる「GaN」(窒化ガリウム)。しかし、実用化が進むSiCと比べて、GaNの開発は遅れているように見える。GaNを採用すると、SiCと同様に電力変換時の損失を低減できる。さらに、SiやSiCよりも高速なスイッチングが可能だ。これは電源の小型化に大いに役立つ。しかし、ノーマリーオフ動作が難しいという欠点もある。こちらは電源には向かない特性だ。GaNの長所を伸ばし、欠点をつぶす、このような開発が進んでいる。 太陽光を無駄なく使う、201X年の技術

太陽光を無駄なく使う、201X年の技術

再生可能エネルギーの固定価格買い取り制度が始まり、太陽電池は激しい価格競争に入っている。このようなときこそ、太陽電池の高効率化を忘れてはならない。なぜなら、変換効率を高めることが、低システムコスト実現に役立つからだ。変換効率向上に対してどのような手法が有望で、どこまで高められるのか、解説した。 次世代パワー半導体「GaN」「SiC」が競演

次世代パワー半導体「GaN」「SiC」が競演

「TECHNO-FRONTIER 2013」(2013年7月17〜19日、東京ビッグサイト)では、GaN/SiCを用いた次世代パワー半導体製品の展示が相次いだ。各社のGaNデバイス、SiCデバイスの展示を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

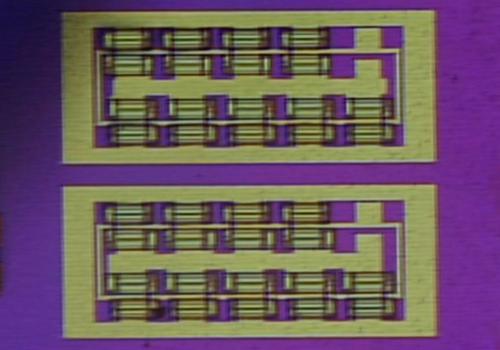

POET TechnologiesのGaAs基板は、トランジスタと光インターコネクトを同一チップ上に集積することができる 出典:POET Technologies

POET TechnologiesのGaAs基板は、トランジスタと光インターコネクトを同一チップ上に集積することができる 出典:POET Technologies