EE Times Japan >

プロセス技術 >

ASMLがEUVリソグラフィ開発の最新状況を公表(2)〜開発の進ちょく状況:SEMICON West 2015リポート(5)(2/2 ページ)

» 2015年08月26日 09時30分 公開

[福田昭,EE Times Japan]

7nm世代のロジックで均一なパターンを形成

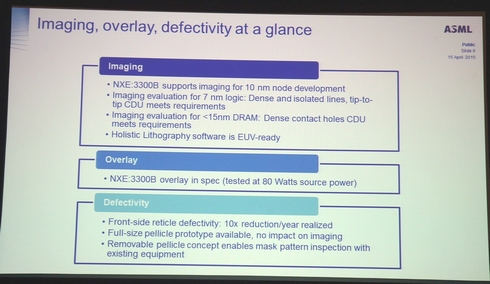

続く2枚目のスライドにも、3つの項目がある。「解像力(Imaging)」、「重ね合わせ精度(Overlay)」、「マスク欠陥(Defectivity)である。

解像力に関しては、「NXE:3300B」は10nm世代の半導体を解像可能になっている。その先の7nm世代のロジックで解像力を評価したところ、疎密が混在する直線と狭い露光領域間のCDU(Critical Dimension Uniformity)は要求仕様を満たした。また15nm未満のDRAMでコンタクトホールを形成したときのCDUも、要求仕様を満たしているとする。

重ね合わせ精度に関しては、出力80WのEUV光源でテストした段階では「NXE:3300B」の製品仕様を満たした。ちなみにASMLのWebサイトによると、NXE:3300Bの重ね合わせ精度(厳密には重ね合わせ誤差)は3nm以下である。

マスク欠陥に関しては、フロント側の欠陥数を1年間に10分の1に下げることができた。ペリクル(レチクルの保護膜)の開発では、フルサイズの試作品が得られるようになった。フルサイズのペリクルは解像度に悪影響を与えていない。また取り外し可能なペリクルにより、既存技術でのマスクパターン検査が可能になった。

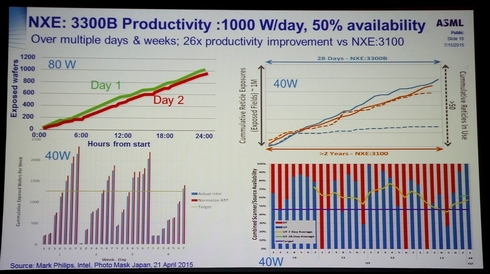

講演者のLercel氏は、具体的なデータのスライドも示した。例えば、24時間の時間経過とともにウエハーの処理枚数が増えていくグラフや時間経過とともに累積の露光回数が増えていくグラフなどをまとめたスライドである。

開発用EUV露光装置「NXE:3300B」による実績データ。左上のグラフは、24時間にウエハーの累積処理枚数が増えていった様子を示したもの。24時間で約1000枚のウエハーを処理できたことが分かる。右上のグラフは、レチクルに対する累積露光回数の推移。NXE:3300Bでは28日間で80万回に達した。前世代のEUV露光装置「NXE:3100」では、80万回に達するまでに約2年を必要とした。左下のグラフは、1週間単位でウエハーの累積処理枚数をまとめたもの。4週間連続で目標枚数に達した。右下のグラフは、稼働時間(アップタイム、青色)と非稼働時間(ダウンタイム、赤色)の比率を日単位で示したもの。黄色の折れ線グラフは、過去7日間の平均稼働率(クリックで拡大)

開発用EUV露光装置「NXE:3300B」による実績データ。左上のグラフは、24時間にウエハーの累積処理枚数が増えていった様子を示したもの。24時間で約1000枚のウエハーを処理できたことが分かる。右上のグラフは、レチクルに対する累積露光回数の推移。NXE:3300Bでは28日間で80万回に達した。前世代のEUV露光装置「NXE:3100」では、80万回に達するまでに約2年を必要とした。左下のグラフは、1週間単位でウエハーの累積処理枚数をまとめたもの。4週間連続で目標枚数に達した。右下のグラフは、稼働時間(アップタイム、青色)と非稼働時間(ダウンタイム、赤色)の比率を日単位で示したもの。黄色の折れ線グラフは、過去7日間の平均稼働率(クリックで拡大)(次回に続く)

関連記事

IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。 ASMLがEUV装置を15台受注、納品先はIntel?

ASMLがEUV装置を15台受注、納品先はIntel?

ASMLが、EUV(極端紫外線)リソグラフィ装置を15台、“米国顧客企業の1社”に納入すると発表し、業界の観測筋の間でさまざまな臆測を呼んでいる。複数の情報筋が、この顧客企業がIntelではないかという見方を示している。 ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

TSMCが、ASMLにEUV(極端紫外線)露光装置2台を発注していたことが明らかになった。TSMCは、EUVリソグラフィによって7nmプロセスの実現を目指すとみられている。2015年末には7nmプロセスを適用したチップのリスク生産が開始される可能性がある。 ニコンが展望する10nm以下のリソグラフィ技術(前編)

ニコンが展望する10nm以下のリソグラフィ技術(前編)

本稿では、リソグラフィ技術の将来を14nm世代から5nm世代まで展望するシンポジウムにおける、ニコンの講演内容を紹介する。同社は、10nm世代にArF液浸露光技術を適用する場合、2つの大きな課題があると指摘した。「EPE(Edge Placement Error)」と「コストの急増」だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

Special SitePR

あなたにおすすめの記事PR