もうコンセプトだけとは言わせない! 待機電力ゼロの不揮発システムLSIへ前進:プロセス技術 不揮発ロジック

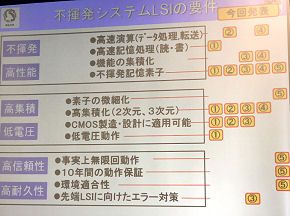

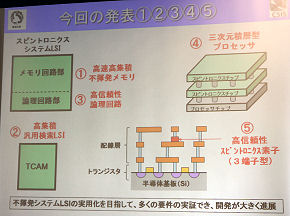

東北大学とNECの研究グループは、スピントロニクス回路を採用した待機電力ゼロの不揮発システムLSIの開発を進めてきた。今回、「不揮発、高性能」、「高集積、低電圧動作」、「高信頼性、高耐久性」という技術要件を満たすべく、5つの要素技術を開発した。

東北大学とNECの研究グループは、使用していないときの消費電力を完全にゼロにできる「待機電力ゼロの不揮発システムLSI」の実用化に大きく貢献する5つの新技術を開発したと発表した*1)。

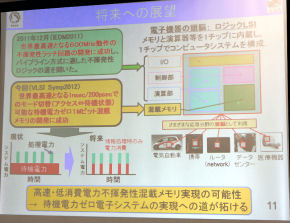

ロジックやアナログ、メモリが混載されたシステムLSIは、デジタルAVやモバイル、PC、サーバといったさまざまな機器において、処理の中心的な役割を担う半導体部品である。同研究グループではこれまでも、「スピントロニクス(磁性素子)」を採用した不揮発ロジックの研究開発を進めており、2011年6月には「システムLSIと呼べる形で、スピントロニクスを使った不揮発ロジックの動作を実証した」という研究成果を発表していた(関連記事:目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証)。

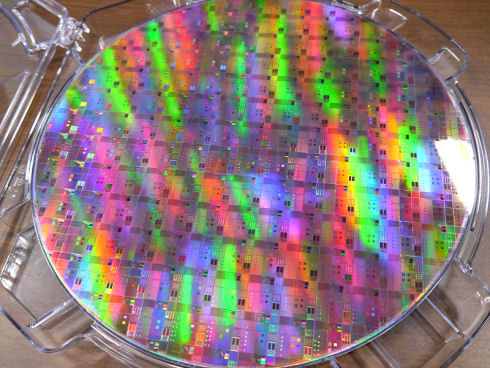

今回の研究成果の意義は、「スピントロニクス回路を採用しつつ、高集積、高速、高信頼という、不揮発システムLSIを実用化する上で欠かせない対策を、多面的に進めたことだ」(東北大学 省エネルギー・スピントロニクス集積化システムセンターのセンター長を務める大野英男氏)という。実際に、開発した幾つかの回路を300mmウエハーに実装し、評価を進めた。

高集積、高速、高信頼へ――

東北大学の大野氏によれば、不揮発システムLSIには「不揮発、高性能」、「高集積、低電圧動作」、「高信頼性、高耐久性」という3つの技術要件がある。今回の新技術群は、この3つの技術要件を満たすことを目的に開発された。具体的には、以下の5つの研究成果である(クリックで、東北大学のニュースリリースにリンクします)。

- 「待機電力ゼロのロジック混載用高速高集積不揮発メモリを開発」

- 「スピントロニクス技術を用いた3次元積層型スピンプロセッサを開発」

- 「スピントロニクス技術を用いた世界最小の待機電力ゼロ、汎用検索集積回路(TCAM)の実証」

- 「3端子型スピントロニクス素子の高信頼性の実証」

- 「スピントロニクス論路集積回路の信頼性を向上する技術を開発」

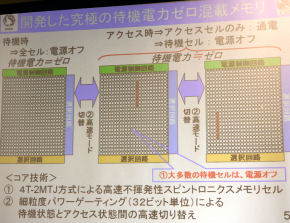

この中で比較的実用化に近いのが、(1)の「待機電力ゼロのロジック混載用高速高集積不揮発メモリを開発」だ。「スマートフォンやモバイル機器向けのシステムLSIを対象に、実用化を狙えるところまで研究は進んでいる。システムLSIのL3キャッシュメモリに匹敵する性能を達成した。もう、“コンセプト止まり”という段階ではない」(東北大学 省エネルギー・スピントロニクス集積化システムセンターの副センター長を務める遠藤哲郎氏)という。

具体的には、4つのトランジスタと2つのスピン注入磁化反転型磁気トンネル接続(MTJ)素子で構成したSRAM互換の高速メモリセルを試作した。容量は1Mビットである。その上で、32ビット単位の細粒度パワーゲーティング動作を実装することで、待機電力のゼロ化とロジック混載メモリに要求される高速アクセスを両立させた。

左は、開発したロジック混載用高速不揮発メモリの動作イメージ。待機時には全メモリセルの電源をオフにし、32ビットの細粒度パワーゲーティングを採用することでアクセス時にも対象セルのみに電力を供給する仕組みだ。右は、2011年の研究成果と今年(2012年)の研究成果の意義をまとめた資料。

左は、開発したロジック混載用高速不揮発メモリの動作イメージ。待機時には全メモリセルの電源をオフにし、32ビットの細粒度パワーゲーティングを採用することでアクセス時にも対象セルのみに電力を供給する仕組みだ。右は、2011年の研究成果と今年(2012年)の研究成果の意義をまとめた資料。アクセス時にもアクセス対象のメモリセルのみに電力を供給し、その他の99.9%のメモリセルは待機セルとして電力を供給しない。モードの切り替えに要する時間は、アクセス状態から待機状態に移るときに0.2ns、待機状態からアクセス状態に移るときに1.0nsである。今後、ハイエンドサーバ向けのシステムLSIへの搭載を狙い、L1キャッシュメモリとL2キャッシュメモリの性能をターゲットにした研究を進めるという。

- ソニーセミコンとTSMC、次世代イメージセンサーで提携 フィジカルAI分野に照準

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- ソニーとTSMCが新たな合弁検討、半導体のファブライト化とフィジカルAI見据え

- ソニーセミコンとTSMCが合弁会社設立を検討

- MetaとAWSが提携 エージェント型AI強化に最新のArmベースチップ「Graviton5」を大量採用

- 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 先端半導体用フォトレジスト技術棟を新設、3つの機能を集約

- Intel、イーロン・マスク氏の「Terafab」構想に参画 次世代AIチップ生産を支援

- Arm Cortex-M33コア搭載の低価格マイコン、ST

関連記事

目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証

目指すは待機電力ゼロの夢のLSI、東北大が磁性素子利用の不揮発ロジックを実証

もはや、従来技術の延長ではこれ以上の消費電力の削減は見込めない。今まさに、半導体チップの基本デバイスの根本的な変革が必要な時期を迎えている。 マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用

マイコンの進化を不揮発メモリが助ける、パナソニックが「ReRAM」を採用

新規の不揮発メモリが次々と最終製品への応用段階に進み始めた。SSD向けの「MRAM」、携帯電話機向けの「PRAM」、そして今度はマイコン向けの「ReRAM」だ。ReRAMは少ない電力で動作し、高密度化も可能な優れた性質を備える。パナニックはReRAMマイコンで、低消費電力が求められるスマートメーターやスマートフォン市場を狙う。 微細化の限界に挑む、Siと新材料の融合で新たな展望も

微細化の限界に挑む、Siと新材料の融合で新たな展望も

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000年代に入り、状況が変わってきた。 不揮発メモリ新時代(前編)

不揮発メモリ新時代(前編)

今後、メモリは全て不揮発になる。機器の機能向上につれて、増えたシステム全体の消費電力を抑えるのに、メモリの不揮発化が役立つからだ。メモリが不揮発化すれば、ほかのメリットも生じる。例えばデジタル家電を瞬時に起動できるようになる。PCの起動やシャットダウン操作が不要になる。 不揮発メモリ新時代(後編)

不揮発メモリ新時代(後編)

現在のDRAMやNAND型フラッシュメモリの用途に向けた次世代不揮発メモリの候補は4種類ある。FeRAM、MRAM、PRAM、ReRAMだ。ただし、どれか1つの不揮発メモリで全用途に対応することは難しそうだ。これはどの不揮発メモリにも何らかの欠点が存在するからだ。後編では不揮発メモリの用途や各不揮発メモリの性能向上策、技術動向について解説する。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長