メモリ関連の論文は“量より質”にシフト:ISSCC 2013プレビュー(2/2 ページ)

勢いづくReRAM

メモリ関連でひときわ注目を集めているのが、東芝とSandiskによる32GビットReRAMに関する論文だ。その試作チップは、24nmプロセス技術を採用して製造しており、セル選択素子としてダイオードを使用しているという。

ReRAMは、データの書き換え可能回数が多く、読み出し/書き込み時におけるビット当たりの消費電力も少ないことから、従来の不揮発性メモリを置き換えるものとして期待を集めている。ただし、その密度については、NAND型フラッシュメモリに遠く及ばない。ISSCCの開催関係者によれば、前回発表されたシングルチップ品の中で最も密度が高かったものを見ると、NAND型フラッシュメモリが最大で128Gビットだったのに対し、ReRAMは64Mビット、PRAMは8Gビットだったという。

またパナソニックも、ReRAMに関する論文を発表する。その論文では、ReRAMにおいて、微細な電気伝導経路を形成する技術や、16nm世代のセルにおいて書き換え回数を向上する技術などについて説明される。

進化を続けるSRAM

SRAMでは、45nmのプロセスノード以降、リーク電流や動作電流の削減が大きな課題となっている。IntelのZhang氏は、「22nm世代以降のプロセス技術でも、引き続きセル面積の縮小と低電圧での動作を実現していくためには、FinFET(立体構造トランジスタ)と完全空乏型SOI(FD-SOI:Fully Depeleted Silicon-on-Insulator)の採用が鍵となる」と述べている。

TSMCは、20nmプロセス技術による112Mビットの6T(6トランジスタ) SRAMに関する論文を発表する。この6T SRAMにおけるビットセルの面積は、過去最小の0.081μm2になるという。4レベルの電源制御技術により、データ保持不良の原因となるリーク電流を65%以上削減したとしている。

帯域幅の問題を解消

メモリ帯域幅も、引き続き拡大していくようだ。ISSCC 2013では、メモリトランシーバ向けとしては過去最高レベルのデータ転送速度を実現する技術が発表される。

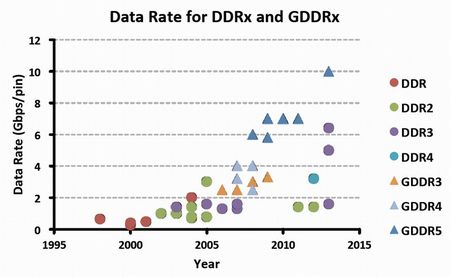

Rambusが発表を予定しているシングルエンドのトランシーバでは、高密度のデュアルランクDIMMモジュール向けに1ピン当たり6.4Gビット/秒(Gbps)の転送速度が実現されているという。同社は、ISSCC 2012でも同様の技術に関する論文を発表していたが、その当時はDDR4における1ピン当たりの転送速度が3.2Gbpsで、今回の半分程度だった。また同社のトランシーバでは、電力効率が1Gbps当たり9.1mWと飛躍的に改善しており、将来的な実用化に向けて必要な水準を既に達成しているという。

Rambusは、論文のプレビューにおいて、「この開発成果によって、われわれの技術が、データセンターのサーバ機器やネットワーキング機器、低消費電力の携帯型機器など、幅広い分野で利用できる可能性を実証することができた。データ転送速度を高めるとともに、DRAMの消費電力を最小限に抑えることで、システムの性能を大幅に向上できるはずだ」と説明している。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長