「ハードとソフトの世界を近づけたい」――OpenCL対応を加速するアルテラの狙い:HPC以外でもFPGAによるOpenCL利用が広がる(2/2 ページ)

幅広い用途で支持される“OpenCL+FPGA”

EETJ FPGAのOpenCL対応を可能にしたSDKの提供開始から1年ほど経過しましたが、市場の反応はいかがでしょうか。

Seynhaeve氏 とても好評だ。OpenCLが主にターゲットとしているハイパフォーマンスコンピューティング(HPC)分野でも採用が進んでいる他、意外にもHPC分野以外でも実績が多く生まれている。

EETJ SDK、コンパイラによりFPGAはGPUなどと同じようにC言語で扱えるようになりましたが、依然としてGPUなどと比べ割高なFPGAが選択される理由は、どのあたりにありますか。

Seynhaeve氏 FPGAが支持されている理由は、効率の良さ、消費電力の低さだ。FPGAは、処理内容に応じて最適なハードウェアを構成し無駄がない。そのため、CPUやGPUに比べ効率が良く、消費電力も抑えられる。

HPC分野は、多くのデバイス、ボードを並べた大規模なシステムが構築される。そうなれば、システムを冷却する空調システムも大規模で電力代が大きくなる。そのため、デバイスコストよりも電力効率が重視されるようになる。もちろん、FPGAよりも最適化が行えるASICの方が効率が良いが、最先端プロセスを使用したASICは多額の開発費、初期コストが掛かる訳であり、多くの用途で現実的な解ではなく、FPGAが選ばれている。

その顕著な例が大規模な並列コンピューティングが必要な「ビットコインの採掘(マイニング)」でのFPGAの採用だ。ビットコインは相場で価値が乱高下するため、せっかく採掘したものの、冷房コストの方が高かったということもあり得る。特にコストにシビアなこのビットコインの採掘でFPGAが利用されていることで、FPGAの利点が分かってもらえるだろう。

また、消費電力だけでなく、性能面でもFPGAは優位性を発揮している。金融システム向けのテストベンチの結果、FPGAはGPUよりも消費電力が半分ながら、処理速度は8倍速いという結果も出ている。そうした結果からも“OpenCL+FPGA”への支持が広がっている。

「SoC FPGA」でHPC分野以外でもOpenCLの応用始まる

EETJ HPC分野以外での、“OpenCL+FPGA”の応用とはどのようなものですか。

Seynhaeve氏 1つは、多機能プリンタ(MFP)だ。MFPは、機能は多いが、各ベンダーともに似た機能を搭載し、差異化が難しくなっている。そのため、MFPベンダーは、新機能を一刻も早く実装し、市場投入したいというニーズがある。これまで、量産数量の多いMFPにはASICが用いられてきたが、ASICの開発期間は18〜24カ月程度は必要で時間がかかる。そこで、短期間で開発可能なOpenCLとFPGAの組み合わせで採用が進んでいる。

もう1つ、面白いHPC以外での採用事例が、自動車の歩行者検知システムだ。これまで歩行者検知はDSPベースのソリューションが多かったが、検知用のカメラの台数が増えるにしたがいDSPだけでは処理が追い付かない状況になり、FPGAへのニーズがあった。DSPに慣れている設計者はFPGAの使いこなしが難しかったが、OpenCL対応SDKによりFPGAの採用が可能になった分野だ。

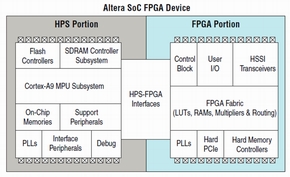

これらHPC以外の分野は共通して、デバイスコストも抑える必要がある。単に、CPUとFPGAの構成では、価格は見合わない。しかし、われわれの高性能なARMプロセッサコアをハードIPとして集積するFPGA製品群「SoC FPGA」により、CPUとハードウェアアクセラレータをシングルチップで実装できる。先に挙げたMFPでは、ローコストFPGA製品である「Cyclone V SoC」を使用しシングルチップで実現している。SoC FPGAにより、従来、OpenCLを使ってこなかった非HPC分野でも、コストに見合う形で、OpenCLを利用できるようになった。

先行している点で数多くの強みを発揮

EETJ “OpenCL+FPGA”の利用拡大もあってか、他のFPGAベンダーもOpenCL対応の動きを活発化していますが、アルテラとしての強みなどはありますか。

Seynhaeve氏 アルテラは先行してOpenCLに取り組んできており、いろいろな面で先行できている。その1つがOpenCL対応で最も基本的で重要な、規格への順守。規格適合テストは8500項目以上あり、簡単ではない。また、OpenCLに関するエコシステムも時間を掛けて広げてきており、アルテラの優位性になっている。最近でもIBMのPOWER マイクロプロセッサ・アーキテクチャを利用したオープンなアライアンスである「IBM OpenPOWER Foundation」に参加して次世代POWERベース・システムに向けた開発に着手するなど、いろいろな企業との連携が図れている。アルテラ製FPGAをベースにした並列コンピューティング、OpenCL向けボード製品も多くの企業から提供されている。

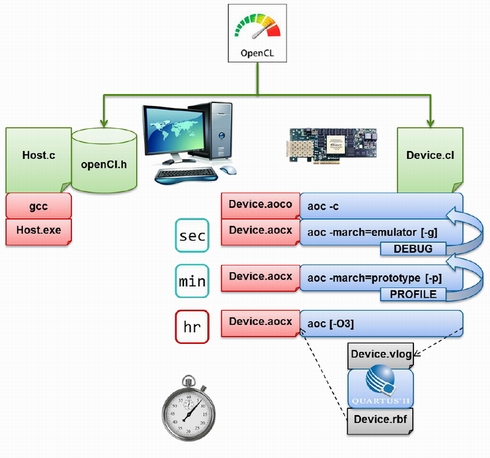

製品や開発環境などでも先行できている。OpenCL対応で重要なC言語からHDLへのコンパイルはどうしても数時間単位の時間が必要になる。数時間も掛かるコンパイルを繰り返して、開発するのは現実的ではない。アルテラのOpenCL SDKは、シミュレータやエミュレータにより、数分間で行える簡易的なコンパイルで、大部分のデバッグ/検証が行える機能を搭載している。こうした機能はアルテラ独自のものであり、大きな強みになっている。

アルテラの提供するOpenCL向けSDKのコンパイルのイメージ。時間単位で掛かるコンパイルだけでなく、数秒、数分で終えられる簡易コンパイルで開発工程の大部分を補える機能を搭載し、「CPUやGPUと同等の開発時間で開発できる」(Seynhaeve氏)という環境を整えている (クリックで拡大) 出典:アルテラ

アルテラの提供するOpenCL向けSDKのコンパイルのイメージ。時間単位で掛かるコンパイルだけでなく、数秒、数分で終えられる簡易コンパイルで開発工程の大部分を補える機能を搭載し、「CPUやGPUと同等の開発時間で開発できる」(Seynhaeve氏)という環境を整えている (クリックで拡大) 出典:アルテラさらに、このほど発表した通り、20nmプロセスで製造される「Arria 10」FPGA&SoCと、14nmトライゲートプロセスで製造される「Stratix 10」FPGA&SoCで、ハードウェア浮動小数点DSPブロックを内蔵した製品を投入する(関連記事:FPGAにハードウェア浮動小数点DSP内蔵、電力効率でGPGPUの上を行く)。より並列コンピューティングの分野で、FPGA、アルテラの優位性が高まるだろう。

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ダメ半導体ベンチャーだったLattice SemiconductorのV字復活劇はPLDとともに

- Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

- 独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

- 飛躍するXilinx、AMDとの因縁も既に始まっていた!?

- FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

- レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

- Alteraの創業によるCPLDの萌芽でプログラマブルロジックはさらなる進化へ

- プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

- プログラマブルロジックの誕生――CPLD前史

関連記事

FPGAにハードウェア浮動小数点DSP内蔵、電力効率でGPGPUの上を行く

FPGAにハードウェア浮動小数点DSP内蔵、電力効率でGPGPUの上を行く

アルテラは、同社製FPGAに内蔵するIEEE754準拠のハードウェア浮動小数点DSPを発表した。まず、20nmプロセスで製造される「Arria 10」FPGA&SoCと、14nmトライゲートプロセスで製造される「Stratix 10」FPGA&SoCで、ハードウェア浮動小数点DSPブロックを内蔵した製品を用意する。DSP性能はArria 10で最大1.5T FLOPS、Stratix 10で最大10T FLOPSを実現できるという。 「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

「今すぐ使えるFPGA」、アルテラが運転支援システムなどを提案

アルテラは、「今すぐ使えるFPGAソリューション」をテーマに、最新のアルテラSoCやFPGAおよび評価ボードを展示した。パートナー製品も含めて、安価な評価キットやOpenCLを用いて設計が可能なFPGAアクセラレータボード、アルテラSoCを活用した自動車の運転支援システムなどのデモ展示が来場者の注目を集めていた。 FPGAも並列コンピューティングの選択肢に、AlteraがOpenCLの取り組み発表

FPGAも並列コンピューティングの選択肢に、AlteraがOpenCLの取り組み発表

極めて高いプロセッシング性能を求めるアプリケーションでは、CPUにGPUやDSPなどのヘテロジニアスな計算資源を組み合わせてCPUの負荷をオフロードする並列コンピューティングの適用が進んでいる。Alteraは、オフロード用資源としてFPGAを選択肢に加える取り組みについて明らかにした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門