「世界最速」のCPU間通信向け56Gビット/秒受信回路――富士通研:プロセッサ/マイコン

富士通研究所は2014年6月、CPUなどのチップ間で56Gビット/秒のデータ通信速度で受信できる回路を開発したと発表した。富士通研では「世界最高速のCPU間通信向け受信回路」としている。

富士通研究所は2014年6月13日、CPUなどのチップ間で56Gビット/秒のデータ通信速度で受信できる回路を開発したと発表した。富士通研では「世界最高速のCPU間通信向け受信回路」としている。

データセンターなどで使用されるサーバなどでは、より大規模な処理を行うため、複数のCPUを接続したシステム構成となっている。その際、処理性能をより高速、大規模化するためには、CPU間のデータ通信をより高速化する必要がある。これまでのCPU間データ通信速度は28Gビット/秒程度であり、現在、これを2倍速めた56Gビット/秒通信の標準化が進められている。

ただ、56Gビット/秒の通信速度に対応するには、高速通信で劣化する信号波形を補償する受信回路の開発が不可欠となっている。具体的には、Decision Feedback Equalize(DFE)と呼ばれる補償回路の処理能力を高める必要がある。

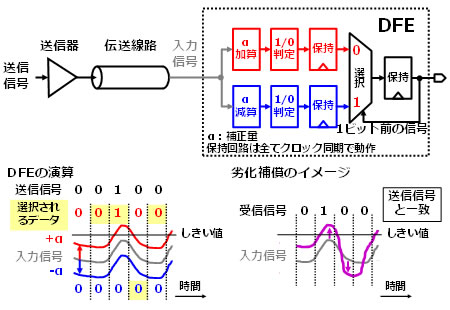

DFEは、1ビット前のビット値に応じた入力信号を補正し、入力信号の変化を強調する仕組みの補償回路であり、実際の回路設計ではあらかじめ補正した候補を2つ用意しておき、ビット値に応じて選択するという動作になる。例えば、1ビット前が「0」の場合、入力信号にプラス方向の補正を加えることで「0」から「1」への変化を強調し、逆に1ビット前が「1」であれば、マイナス方向に補正することで「1」から「0」への変化を強調する。「0」が続く場合には、プラス方向の補正により信号レベルは上がるものの、「0」と「1」を判定するしきい値を越えないため、問題とならない。

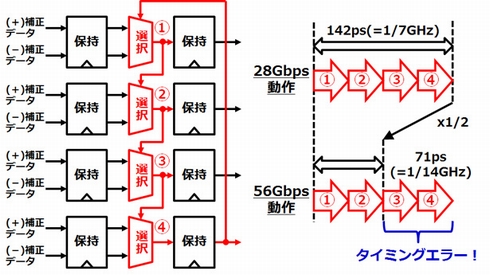

28Gビット/秒に対応するには、通常、このDFEを4個連結させて使用されてきた。4個を1/4周波数、すなわち1/7GHz(142ピコ秒)周期で動作させ4ビット分の補正を行った。このDFE4個構成のまま、56Gビット/秒に適用すると、56Gビット/秒の1/4周期は1/14GHz(71ピコ秒)周期であり、半分の2ビット分の補正までしか収められず、タイミングエラーとなる。

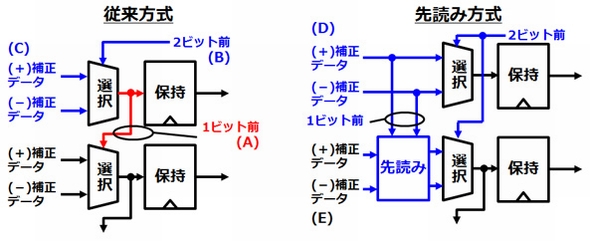

そこで富士通研は、1ビット前の選択結果から得られる候補2つをあらかじめ計算しておき、2ビット前のビット値が決定すると1ビット前のビット値と現在のビット値を同時に決定することで並列処理が可能な先読み方式を新たに考案した。

先読み方式は、1ビット前の選択回路の入力信号(+/−補正データ)と現在の選択回路の入力信号(+/−補正データ)を先に先読み回路で組み合わせて選択回路の候補をあらかじめ算出しておくもの。これにより、1ビット前の選択回路の結果を使わずに、2ビット前の選択回路の結果のみで補正処理が行える。なお、従来方式では、1ビット前の選択回路の結果は、2ビット前の選択回路の結果と1ビット前の選択回路の入力信号(+/−補正データ)の組み合わせ回路で補正処理を行った。

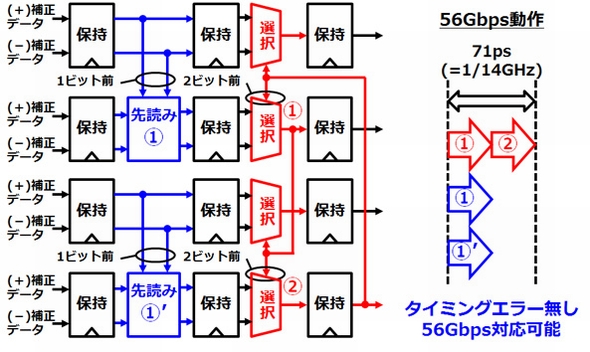

またDFEの1ビットおきに適用した複数の先読み回路は、独立に動作できる。今回、選択回路と先読み回路の間に保持回路を挿入し、各保持回路の入出力を同期させることで、並列処理を可能にしている。

先読み回路の演算時間は、選択器の選択時間とほぼ同じであるため、全体の演算時間は2ビット前のデータから決定する選択器の数に依存し、4ビット構成の場合、選択器は2個となる。これにより、56Gbpsの4分の1周期である71ピコ秒に演算を収められ、結果、従来の2倍の通信速度である56Gbpsでのデータ受信が可能になった。

富士通研では、開発した技術により「CPUの性能が倍になっても、ピン数を増やすことなくCPU間通信を広帯域化することができ、CPUを多数接続した大規模システムでの性能向上に大きく貢献することが期待される。また、光モジュール通信の規格であるOIF標準規格にも対応でき、OIF-CEI-28Gの光モジュール通信で400Gbpsイーサネットを構築する場合に比べて並列動作する回路数(レーン数)を半分にすることができるため、光モジュールの小型化による低電力化やシステム全体の高性能化も期待される」としている。なお、実用化時期については2017年3月期を目指している。

関連記事

カーボンナノチューブを使った「NRAM」の基本動作を実証

カーボンナノチューブを使った「NRAM」の基本動作を実証

中央大学の竹内健教授らのグループは2014年6月12日、米国のNanteroと共同でカーボンナノチューブを用いた半導体メモリ「NRAM」に最適な書き込み方法を開発し、140nmサイズの単体素子によって基本動作を実証したと発表した。 富士通研、CPU間クロック伝送回路の電力を75%削減する技術を開発

富士通研、CPU間クロック伝送回路の電力を75%削減する技術を開発

富士通研究所とFujitsu Laboratories of Americaは2013年6月14日、CPU間の高速データ通信回路の低電力化を実現するクロック伝送技術を開発したと発表した。サーバなどに搭載されるCPU間のクロック伝送回路の消費電力を75%削減できるという。 CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発

CPU間データ通信速度で32Gbpsを達成、富士通研が新たな送受信回路を開発

富士通研究所は、CPU間のデータ通信速度を従来比で約2倍となる32ギガビット/秒(Gbps)に高速化できる送受信回路を開発した。次世代サーバ向けCPUに適用し、2014年ごろの実用化を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

補償回路「DFE」の仕組み 出典:富士通研究所

補償回路「DFE」の仕組み 出典:富士通研究所 従来のDFEの実際の構成と56Gbp動作時の課題 出典:富士通研究所

従来のDFEの実際の構成と56Gbp動作時の課題 出典:富士通研究所 先読み方式の原理 出典:富士通研究所

先読み方式の原理 出典:富士通研究所 新規構成のDFEとその効果 出典:富士通研究所

新規構成のDFEとその効果 出典:富士通研究所