ザイリンクス、28nm世代FPGAの低コスト・低電力ファミリの出荷を開始:プログラマブルロジック FPGA(2/2 ページ)

2.78Tビット/秒帯域幅のFPGAも出荷済み

ザイリンクスはこの他、高性能の有線通信アプリケーション向けに開発した28nm世代のハイエンドFPGA「Virtex-7 H580T」についても説明した。この品種については、出荷開始を2012年5月30日(米国時間)に発表済みだった。

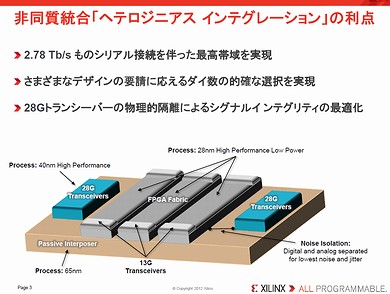

Virtex-7 H580Tは、Virtex-7のうち、最大28Gビット/秒で動作する高速シリアルトランシーバ(SERDES:シリアライザ/デシリアライザ)を16チャネルと、13.1Gビット/秒のSERDESを72チャネル搭載した品種である。このデバイス単体で、入出力帯域幅は2.78T(テラ)ビット/秒に達する計算だ。[28Gビット/秒×16チャネル]+[13.1Gビット/秒×80チャネル]=1391Gビット/秒になり、入力出力の2方向分で2倍すると2782Gビット/秒になる。

Virtex-7 H580Tは、3次元実装技術でFPGAチップとSERDESチップを単一パッケージに統合してり、このデバイス1個で入出力帯域幅は2.78T(テラ)ビット/秒に達する。出典:ザイリンクス (クリックで画像を拡大)

Virtex-7 H580Tは、3次元実装技術でFPGAチップとSERDESチップを単一パッケージに統合してり、このデバイス1個で入出力帯域幅は2.78T(テラ)ビット/秒に達する。出典:ザイリンクス (クリックで画像を拡大)FPGAのチップと28Gビット/秒のSERDESチップを個別に製造し、「スタックド シリコン インターコネクト(SSI)」と呼ぶ3次元実装技術を適用して単一のパッケージに収めた、マルチパッケージ品である。SSIは、樹脂材料を使うパッケージ基板の上に、Si(シリコン)材料を使った支持基板(インターポーザ)を載せ、その上に複数のベアチップを同一平面に並べて実装する構造を採る。ザイリンクスは既に、このSSIを使って複数のFPGAチップをまとめて単一のパッケージに封止し、ロジックセルの規模を拡張した「Virtex-7 2000T」を出荷済みだが、FPGAチップとSERDESチップというように異種の(ヘテロジニアスな)チップをまとめたのはこれが初めて。

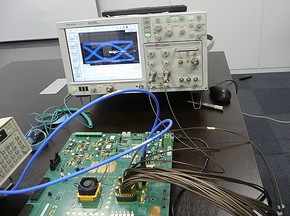

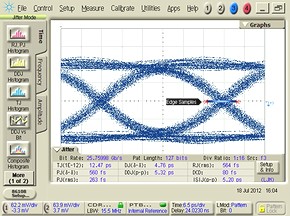

左図は、ザイリンクスが見せたVirtex-7 H580Tの実動デモの様子。Virtex-7 H580Tのサンプル品を実装した評価ボード上で、同デバイスが搭載する28Gビット/秒のSERDESを実際に動作させながら、アイパターンを観測したりビット誤り率を測定したりしている。ボード上、ファンが取り付けられたデバイスがVirtex-7 H580Tである。右図は、広帯域オシロスコープで補足したアイパターン。アイの開口率やジッターの計測値が読み取れる。 (クリックで各画像を拡大)

左図は、ザイリンクスが見せたVirtex-7 H580Tの実動デモの様子。Virtex-7 H580Tのサンプル品を実装した評価ボード上で、同デバイスが搭載する28Gビット/秒のSERDESを実際に動作させながら、アイパターンを観測したりビット誤り率を測定したりしている。ボード上、ファンが取り付けられたデバイスがVirtex-7 H580Tである。右図は、広帯域オシロスコープで補足したアイパターン。アイの開口率やジッターの計測値が読み取れる。 (クリックで各画像を拡大)競合のアルテラも、3次元実装技術を適用してFPGAとASICやメモリ、ASSP、DSP、マイクロプロセッサのベアチップを1つのパッケージに統合する取り組みを進めており、テスト用デバイスを開発済みだと発表している。これに対しザイリンクスは、「ヘテロジニアス構成のデバイスを製品として出荷したのは今回のVirtex-7 H580Tが世界初だ。SSIを適用したヘテロジニアス構成についても、Virtex-7のこのシリーズではFPGAとSERDESの組み合わせしか考えていないが、それ以外ではメモリチップの混載といったさまざまな応用を検討している」と述べている。

- AMDのPLD事業を買収し意気軒高のLattice SemiconductorがFPGA参入で崖っぷちに

- ダメ半導体ベンチャーだったLattice SemiconductorのV字復活劇はPLDとともに

- Xilinxの訴訟や3度のIPO延期を耐えたActelは晴れてFPGAベンダーの3位グループに

- 独創的なロジック記憶手法で違いを見せつけたActelはいかにして誕生したのか

- 飛躍するXilinx、AMDとの因縁も既に始まっていた!?

- FPGAを発明したXilinxとセイコーエプソンの知られざる深イイ関係

- レナード・ニモイがAlteraのCPLDを隆盛に導いた!? Xilinxとの競合も始まる

- Alteraの創業によるCPLDの萌芽でプログラマブルロジックはさらなる進化へ

- プログラマブルロジック市場を創り出した「PAL」は逆転のひらめきから生まれた

- プログラマブルロジックの誕生――CPLD前史

関連キーワード

ザイリンクス | FPGA | 消費電力 | アルテラ | 28nmプロセス | 実装技術(エレクトロニクス) | プロセス技術(エレクトロニクス) | 45nmプロセス | ASIC | 基地局 | DSP(Digital Signal Processor) | プログラマブルロジック(エレクトロニクス) | オシロスコープ | トランジスタ

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待