第36回 「相対ばらつき」も考慮してBand Gap Referenceを設計:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

バイアス電流でオフセット電圧の悪影響を防ぐ

それではオフセット電圧(Voff)の悪影響をどのように防ぐのでしょうか。図4のC領域の位置に注目してください。前述のとおり差電圧(Va−Vb)がマイナスとなり、BGR回路の基準部に電流が流れなくなると危険ということなのです。

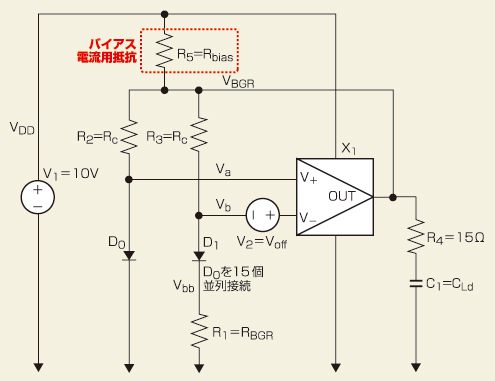

そうなると、最も簡単な対策は、BGR回路の基準部に電流が必ず流れるようにすることです。このための最も手軽な方法は、図5のようにバイアス電流用抵抗(Rbias)を追加することです。ただ、この方法が使えるのはオペアンプの出力段がp型MOSFETだけで構成されていて、電流が吐き出しの状態だけになることが条件になります。前回の図4に示した通り、今回使ったオペアンプは出力段(前回の図4のX2)がp型MOSFETになっています。

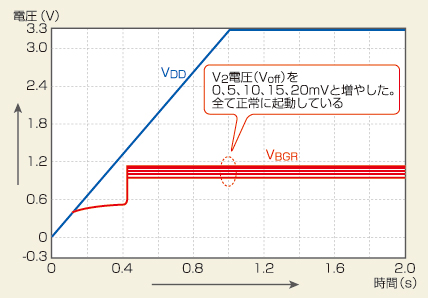

上の図4を見ると、0.1mAも流せば十分にオフセット電圧を相殺できることが分かります。従って、VBGRが0Vでも0.1mA以上を流すためには、Rbiasの値を電源電圧3.3V/0.1mA=33kΩ以下にすれば良いことが分かります。図6が改善を加えたBGR回路の起動特性です。バイアス電流用抵抗を挿入する方法は最も簡単なのですが、電源電圧(VDD)に載った雑音成分の影響を受けやすくなるといった欠点があります。実際のBGR回路ではさらに工夫をしていて、抵抗の代わりにスイッチを使い、BGR回路が正しく起動できるとスイッチを切断し、余計な特性劣化を防いでいます。

これまで、「Analog ABC(アナログ技術基礎講座)」と題した本連載では、アナログ回路の基礎をさまざまな切り口で解説してきました。3年に及ぶ連載も今回でいったん区切りを付けたいと思います。アナログの世界は奥深く、紹介できていないことがまだ残っています。またいずれ再開できればと考えています。次回が最終回になります。

Profile

美齊津摂夫(みさいず せつお)

1986年に大手の通信系ハードウエア開発会社に入社し、光通信向けモジュールの開発に携わる。2004年に、ディー・クルー・テクノロジーズに入社。現在は、同社の常務取締役CTO(最高技術責任者)兼プラットフォーム開発統括部長を務めている。「大学では電気工学科に所属していたのですが、学生のときにはアナログ回路の勉強を避けていました。ですから、トランジスタや電界効果トランジスタ(FET)を使ったアナログ回路の世界には、社会人になってから出会ったといっていいと思います。なぜかアナログ回路の魅力に取りつかれ、23年目になりました」。

- −総集編−アナログ回路の入門はここで決まり!! 計36回の連載を一覧で解説

- −最終回−若手エンジニアへのエール〜この激動の時代、回路設計者として生きるということ〜

- 第36回 「相対ばらつき」も考慮してBand Gap Referenceを設計

- 第35回 あの手この手でBand Gap Referenceの電源雑音対策

- 第34回 温度変化の“相殺”でBand Gap Referenceの特性改善

- 第33回 Band Gap Referenceの原理を出発点から解説

- 第32回 MOSFETのオペアンプを改善〜裏返し回路で入出力特性向上〜

- 第31回 MOSFETのオペアンプを改善〜FETを変えず回路の工夫で特性向上〜

- 第30回 MOSFETのオペアンプを改善〜FET寸法の調整で入出力特性を向上〜

- 第29回 MOSFETを使ってオペアンプを設計

- 第28回 カレントミラーで2つのMOSFETの歩調を合わせる

- 第27回 n型MOSFETにp型追加して利得向上

- 第26回 MOSFETで増幅器を設計(2)

- 第25回 MOSFETで増幅器を設計(1)

- 第24回 MOSFETの基本を理解する

- 番外編 電源フィルタの設計に悪戦苦闘、雑音を抑えるはずが発振状態に…(後編)

- 番外編 電源フィルタの設計に悪戦苦闘、雑音を抑えるはずが発振状態に…(前編)

- 番外編 基板から不可解な音が聞こえる、コンデンサが震えていた理由は…

- 第20回 差動対がオペアンプに変身(5)〜コンデンサを追加して位相補償〜

- 第19回 差動対がオペアンプに変身(4)〜オープン特性を1次傾斜へ〜

- 第18回 差動対がオペアンプに変身(3)〜入出力範囲をエミッタ接地で広げる〜

- 第17回 差動対がオペアンプに変身(2)〜能動負荷を交流解析〜

- 第16回 差動対がオペアンプに変身(1)〜能動負荷で利得を高める〜

- 第15回 差動対の利得を理解する

- 第14回 差動対を手を動かして理解する

- 第13回 アナログ回路に不可欠な差動対

- 番外編 アナログ回路設計のエンジン(後編)

- 番外編 アナログ回路設計のエンジン(前編)

- 第10回 エミッタ接地回路のサプリメント 〜 ベース接地回路 〜

- 第9回 エミッタ接地回路のサプリメント 〜 エミッタ・フォロア 〜

- 第8回 エミッタ接地回路にばらつき対策施す

- 第7回 エミッタ接地回路の温度対策

- 第6回 エミッタ接地回路の定数を決める

- 第5回 トランジスタには接続方法が3つ

- 第4回 基本現象を応用して回路設計 〜 フィルタ 〜

- 第3回 回路はすべてオームの法則から(後編)

- 第2回 回路はすべてオームの法則から(前編)

- 第1回 楽しいアナログ回路設計

- 執筆者インタビュー「空想する、結果を思い描く」

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

図5 相対ばらつきに対する改善を加えたBGR回路 相対ばらつきに起因したオフセット電圧の悪影響をバイアス電流で防ぎます。

図5 相対ばらつきに対する改善を加えたBGR回路 相対ばらつきに起因したオフセット電圧の悪影響をバイアス電流で防ぎます。 図6 改善を加えたBGR回路の起動特性 オフセット電圧が増えたときでも、正常に起動できていることが分かります。

図6 改善を加えたBGR回路の起動特性 オフセット電圧が増えたときでも、正常に起動できていることが分かります。