EE Times Japan『プロセス技術』

「EE Times Japan『プロセス技術』」の連載記事一覧です。

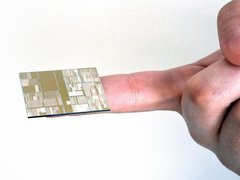

EUVとSiGeチャネルで:

IBM Researchが、EUV(極端紫外線)リソグラフィとSiGe(シリコンゲルマニウム)チャネルを使用した7nmプロセス試作チップを発表した。IBM Researchはここ最近、最先端プロセスの研究開発成果の発表に力を入れていて、7nmプロセスの技術開発に自信を示してきたIntelに迫る勢いを見せている。

プロセス技術:

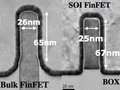

FinFETとFD-SOI(完全空乏型シリコン・オン・インシュレータ)の両方の技術を、用途などに合わせて採用しようと考える半導体メーカーが増えているという。ファウンドリ側も、こうしたニーズに柔軟に対応することが必要になってくる。

「Cortex-A」を最先端プロセスで実証へ:

UMCは、14nm FinFETプロセスの導入に向け、ARMやSynopsysと提携し、同プロセス向けのプラットフォーム構築に取り組む。まずは、ARMのプロセッサコア「Cortex-A」を14nm FinFETプロセスで実証する予定だ。

「ムーアの法則」から抜け出す時?:

GLOBALFOUNDRIESは、22nm FD-SOI(完全空乏型シリコン・オン・インシュレータ)プロセスの導入について、2016年末の量産開始を目指すという。同社は「28nm FinFETと同程度のコストで、14nm FinFETと同等の性能を実現できる」としている。

プロセス技術:

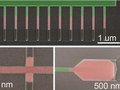

IBMがIII-V族化合物半導体を使ったFinFETの開発成果を積極的に発表している。IBMは、局所横方向エピタキシャル成長(CELO)技術により、シリコンおよびSOI基板の両方に、通常のCMOSプロセスで、InGaAsのFinFETを形成したと発表した。

プロセス技術:

IBM研究所が、Si(シリコン)とIII-V族化合物半導体を組み合わせたナノワイヤを形成する技術を発表した。独自の「TASE(Template-Assisted Selective Epitaxy)」という技術を使って形成する。TASEで作成したInAs(インジウムヒ素)のナノワイヤは、5400cm2/Vsの電子移動度を達成したという。「ムーアの法則」を継続させる鍵になるかもしれない。

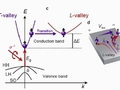

プロセス技術:

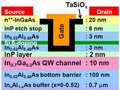

Intelは10年近くにわたり、量子井戸電界効果トランジスタ(QWFET)の研究を進めてきた。ある半導体アナリストは、Intelの10nmチップは、III-V族半導体、具体的にはInGaAs(インジウム・ガリウム・ヒ素)とGe(ゲルマニウム)を用いたQWFETになると予測している。

プロセス技術:

Samsung Electronics(サムスン電子)の最新スマートフォン「Galaxy S6」には、14nm FinFETを適用したプロセッサが搭載されている。同社は、14nm FinFETの生産量において、Intelに次ぐ第2位のポジションを確保したい考えだ。Samsung Semiconductorの幹部は、14nmプロセスへの移行を決断するのは、たやすいことではなかったと振り返る。

プロセス技術:

TSMCは、16nmプロセス以降のロードマップを明らかにした。まずは2015年半ばに、16nm FinFET+を適用したチップの量産を開始する。2016年には、10nmチップの生産工場の建設にも着手する。

プロセス技術:

Qualcommは、米国で開催された「International Symposium on Physical Design(ISPD)」で、同社の3次元SoCの技術動向について語った。TSV(シリコン貫通ビア)を使わずに積層することで、小型化と歩留まりの向上を実現したいという。

プロセス技術:

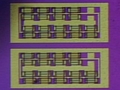

FinFETプロセスを採用したチップは、既に100種類以上がテープアウトされているという。以前は、プロセス技術ではIntelが突出していたが、現在はTSMCやSamsung ElectronicsなどのファウンドリもIntelとの差を縮めてきていて、接戦が繰り広げられている。

ビジネスニュース 企業動向:

TSMCは、10nmプロセスを適用したチップの製造を2017年に開始する。同社は「インテルの10nmチップと同等レベルの性能を実現できると見ている。10nmプロセスで、インテルとの技術的なギャップを埋められるだろう」と述べている。

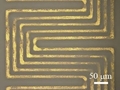

プロセス技術 印刷エレクトロニクス:

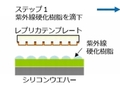

キヤノンは、開発中のナノインプリント技術を用いた半導体製造装置について、2015年中の製品化を目指している。同装置は解像度10nm台の微細加工に対応することが可能である。まずはフラッシュメモリの製造ラインへの導入を予定している。

プロセス技術:

大日本印刷(以下、DNP)は2015年2月19日、20nmレベルの半導体製造プロセスに対応したナノインプリントリソグラフィ(以下、NIL)用のテンプレート(型)の生産体制を構築し2015年にも量産を開始すると発表した。

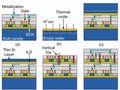

IEDM 2014:

米国で開催された「IEDM(International Electron Devices Meeting)2014」。Intelの14nm FinFETプロセスやTSMCの16nm FinFETなどの開発状況をはじめ、多くの論文が発表された。IEDM 2014のリポートを数回にわたってお届けする。

プロセス技術:

TSMCが、ASMLにEUV(極端紫外線)露光装置2台を発注していたことが明らかになった。TSMCは、EUVリソグラフィによって7nmプロセスの実現を目指すとみられている。2015年末には7nmプロセスを適用したチップのリスク生産が開始される可能性がある。

SEMICON Japan 2014 開催直前情報:

ニコンは、現行機種に比べて重ね合わせ精度とスループットをさらに高めた露光装置「ArFスキャナー NSR-S322F」を発表した。最先端LSIの量産ラインに向ける。

プロセス技術:

Samsung Electronics(サムスン電子)が、ARM主催のイベントで14nm世代のFinFETプロセス技術を適用したチップを発表した。TSMCもその直前に16nm FinFETプロセスを用いたARM「Cortex-A57」の検証を行っているが、ある専門家は、16/14nm FinFETの性能については、SamsungとTSMCは互角だとみている。

プロセス技術:

POET Technologiesは、ムーアの法則を続ける鍵になる材料として、GaAs(ガリウムヒ素)を挙げている。高いスイッチング周波数を実現できるだけでなく、光回路と論理回路を同一チップに集積できるという利点もある。

プロセス技術:

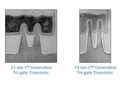

Intelが14nmプロセスを用いたCPU「Core M」(開発コード名「Broadwell-Y」)の概要を発表した。同社にとっては、22nmプロセスの「Haswell」に続き、第2世代となるFinFET(「トライゲートトランジスタ」)である。

プロセス技術:

ケンブリッジ大学キャヴェンディッシュ研究所の岡本尚也氏らは、ガリウムヒ素(GaAs)中で、スピンホール効果の電気的制御が可能であることを実証するとともに、その変換効率をこれまでに比べて最大40倍向上させることに成功したと発表した。

プロセス技術 EUV:

IBMが2014年7月に発表した、EUV(極端紫外線)リソグラフィスキャナーに関する最新テストの結果を、いぶかしむ業界関係者が少なくない。今回のIBMのテスト結果は、EUVの実用化に向けてどのような意味を持つのだろうか。

プロセス技術 EUV:

IBMは2014年7月、ASML製の最新のEUV(極端紫外線)リソグラフィシステムの試験初日に「予想以上の結果を得た」と発表した。スキャナー「NXE3300B」に44Wの光源を用いて、安定した速度(34ウエハー/時)を保って、24時間で637枚のウエハーを作り出したという。

7nm以降の微細加工デバイス実現へ:

IBMは、7nm以降の半導体微細加工技術と、シリコンに代わる新材料によるチップデバイス技術の開発を主とした研究開発を実施すると発表した。今後、5年間で30億米ドル(約3000億円)を投資するという。

課題は山積だが、着実に前進:

最新のEUV(極端紫外線)リソグラフィ装置の予備試験で、40Wの光源を用いて1日当たりウエハー100枚を処理することに成功した。リソグラフィ技術は、EUVでも液浸でも課題は山積している。だが、今回の試験結果は、EUV技術では大きな進展だといえる。

プロセス技術 印刷エレクトロニクス:

物質・材料研究機構(以下、NIMS)や岡山大学らの研究チームは、室温の大気中で印刷プロセスを用い、有機薄膜トランジスタ(TFT:Thin-Film Transistor)を形成することに成功したと発表した。フレキシブル基板上に有機TFTを形成したところ、従来の有機TFTに比べて高い移動度を達成した。今回の研究成果を用いると、大面積の紙や布、さらには人間の皮膚など生体材料の表面にも、半導体素子を形成できる可能性を示した。

プロセス技術:

ルネサス エレクトロニクスとIMECは、LTE-advancedなど次世代無線規格に向け、28nm CMOS技術を用いたRFレシーバとA-Dコンバータを開発した。

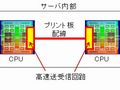

プロセス技術:

富士通研究所とFujitsu Laboratories of Americaは2013年6月14日、CPU間の高速データ通信回路の低電力化を実現するクロック伝送技術を開発したと発表した。サーバなどに搭載されるCPU間のクロック伝送回路の消費電力を75%削減できるという。

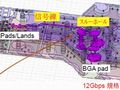

プロセス技術:

ルネサス エレクトロニクスは、LSIと実装基板の間に生まれるインピーダンス差による信号劣化をパッケージ基板内に存在する寄生容量をコントロールして抑える技術として、25Gビット/秒の高速なデータ伝送にも対応する手法を開発した。既に新技術を適用したASICの設計を進め、早ければ2014年にも新技術を搭載したLSIの生産を実施する。

プロセス技術:

新エネルギー・産業技術総合開発機構(NEDO)と超低電圧デバイス技術研究組合(LEAP)は、動作電圧が0.4V以下のロジックLSIやメモリを実現できる技術を開発した。これらの技術を使ったLSIを搭載した機器は、消費電力を1/10に低減できる可能性がある。

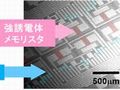

プロセス技術:

パナソニックは、アナログデータを記憶、再生できる「強誘電体メモリスタ」をCMOS回路上に形成することに成功したと発表した。

プロセス技術 不揮発ロジック:

NECと東北大学は、スピントロニクス技術のロジックLSI分野への応用の道を開く2つの開発成果を発表した。2者は、「今回の開発成果をさらに進化させ、2017年頃には商用デバイスに技術を反映させたい」とする。

プロセス技術:

最先端のプロセス技術の開発に注力するIntel。同社は現在、10nmプロセスの開発を行っているが、それ以降のプロセスについては「先行きが見えない」との見解を示している。

プロセス技術:

14nmプロセス技術を確立することは、設計者たちが予想していたよりも、はるかに難しいようだ。プロセスの微細化が進むに連れて、リーク電流の増加などの課題が浮き彫りになった。IBMのエンジニアは、「14nm世代では、これまでの対応策が通用しなくなる」との見解を述べている。

プロセス技術:

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。

プロセス技術:

GLOBALFOUNDRIESが、FD-SOIプロセスによるチップの量産開始時期を明らかにした。2013年第1四半期中に同プロセス用のPDKの供給を始め、2014年上半期には大量生産を開始する予定だという。

プロセス技術:

Samsung ElectronicsとGLOBALFOUNDRIES(GF)は、14nmプロセスでの製造開始に向けてデッドヒートを繰り広げている。一方、IBMは、半導体業界のより長期的な発展を見据え、EUVリソグラフィ装置の開発を進めている。ただし、現在のところ芳しい進展は見られていない。EUVリソグラフィ技術の実用化は、7nm世代以降になる見通しだ。

プロセス技術:

Molecular Imprintsは、同社のリソグラフィ装置「Imprio 450」が、ある半導体メーカーに採用されたことを明らかにした。同製品は450mmウエハーによる半導体チップの製造に対応しているという。同社は「Imprio 450により、450mmウエハーへの移行を、少なくとも2年は早められる見込みだ」と主張している。

プロセス技術:

半導体製造技術のロードマップでは、193nmリソグラフィに限界が来たら、157nmフォトリソグラフィへと移行するはずだった。しかし、実際に普及したのは193nmの液浸リソグラフィであった。次の技術として名前が挙がるのはEUVだが、「この技術が実際に商業用途で利用されるかどうかは定かではない」と指摘する声がある。

プロセス技術:

米カリフォルニア州で開催された半導体素子の国際学会「IEDM 2012」では、IBMとIntelが22nmプロセス技術に関する論文を相次いで発表した。22nmプロセスの量産体制に入っているという意味では、優位なのはやはりIntelだろうか。

プロセス技術:

STは、28nmプロセスを適用したFD-SOIの試作品を生産する準備が整ったと発表した。同社は、「FD-SOIは、プレーナ型バルクCMOSやFinFET CMOSなどに比べて、性能や消費電力、製造性の間のトレードオフが少ない」と主張している。

プロセス技術 印刷エレクトロニクス:

PragmatIC Printingは、印刷技術を用いて、柔軟性を持つ素材上にロジック回路を構築する技術の開発に取り組んでいるプリンテッドエレクトロニクス企業である。同社は2012年11月、その技術を適用した製品用のパイロット製造ラインの稼働を開始したと発表した。2013年には、年間1000万個以上の製品を製造可能だという。

プロセス技術:

28nm世代以降のプロセス技術では、フォトマスク上のナノレベルの欠陥でさえも歩留まりに影響することがある。KLA-Tencorは、28nm世代以降のプロセスのレチクルを監視する検査装置を発表した。

プロセス技術 不揮発ロジック:

東北大学とNECの研究グループは、スピントロニクス回路を採用した待機電力ゼロの不揮発システムLSIの開発を進めてきた。今回、「不揮発、高性能」、「高集積、低電圧動作」、「高信頼性、高耐久性」という技術要件を満たすべく、5つの要素技術を開発した。

記事ランキング

- 「Switch 2」を分解 NVIDIAのプロセッサは温存されていた?

- RISC-V移行の流れ、欧州では「もう止められない」

- 「やっぱりルネサスだと言われないと」 柴田CEOが原点回帰を強調

- 「Rapidusを支援したい」 VCに転身のPat Gelsinger氏、日米の協業に意欲

- SiCパワーデバイス市場は年率20%で成長、30年に103億ドル規模に

- 「N2」SRAMの歩留まりは90%以上 技術開発も好調のTSMC

- トヨタの中国向け新型BEV、ローム製SiC MOSFETを搭載

- 2nm半導体設計基盤でRapidusとシーメンスが協業

- 台湾Innolux子会社がパイオニアを1636億円で買収へ

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?