Intelの新型CPU「Ivy Bridge」を早速解剖、3DトランジスタのTEM画像公開:製品解剖 プロセッサ/マイコン

UBM TechInsightsは、まだ公式発売前のIntelの「Ivy Bridge」を入手し、分析に着手した。Ivy Bridgeは、Intelが22nmプロセスで3次元構造のトランジスタを使って製造する新型プロセッサである。今回は初期の分析結果の一部として、チップ写真と断面画像が公開された。

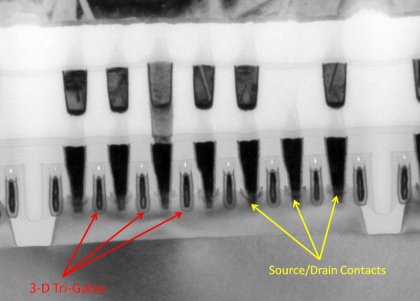

Intelが最先端の半導体プロセス技術で製造する新型CPU「Ivy Bridge」が早速、解剖された。Ivy Bridgeは、Intelが22nm世代のプロセス技術を初めて適用するチップで、3次元ゲート(Tri-Gate)構造のトランジスタ技術を採用する。このチップの分析を手掛けたのは米EE Times誌と同じくUnited Business Mediaの傘下にある技術情報サービス企業のUBM TechInsightsである。同社は今回、初期の分析結果の一部として、透過型電子顕微鏡(TEM)によるIvy Bridgeの断面画像と、ダイ(ベアチップ)の写真を公表した。

Ivy Bridgeは、Intelがまだ公式には発売していないチップだ。一部のWebメディアは、Intelが早ければ4月29日にもIvy Bridgeを公式に発売するという見方を示している。ただ、7月まで発売がずれ込むと伝えるリポートもある。Intelの広報担当者は、Ivy Bridgeの公式発売は「もうすぐだ」と述べ、「2011年の終盤から量産を続けている」と付け加えた。

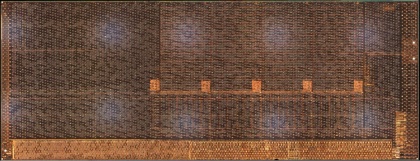

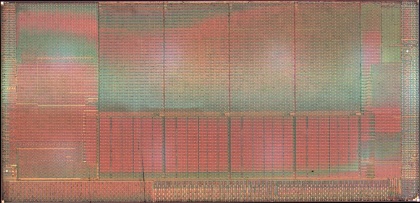

UBM TechInsightsが入手したIvy Bridgeは、マレーシアでパッケージングされたもので、「3.3GHz Core i5-3550」とマーキングされている。同社が測定したところ、このチップのダイサイズ(ベアチップの面積)は170mm2だった。Intelの既存CPU「Sandy Bridge」で208mm2の「Core i7 2600K」に比べると小型化している。

UBM TechInsightsはこの初期の分析で、Ivy Bridgeに集積されたSRAMアレイのゲートピッチが90nmであることを確認した。また同社は、ロジック回路部のゲート長が22nmであることも確かめたという。

現代の半導体業界では一般に、あるプロセス世代を厳密に命名するのは簡単ではない。専門家も、それは「アートとサイエンスの両方にまたがる問題だ」と指摘する。Intelの社内でさえ、あるチップのプロセス世代を命名する際には、さまざまなゲート長のうちいずれを使うかで議論が起きる。

半導体業界の関係者の多くは、次世代の主流となるプロセス世代は28nmだとしてきた。FPGAの大手ベンダーであるAlteraとXilinxは既に28nm世代のFPGAを製造しているし、AMDとQualcommも28nmのチップを製造中だ。各社ともに、GLOBALFOUNDRIESやTSMCといった半導体ファウンドリ企業のプロセスを利用する。

これらに対し、Intelの22nm技術は、「FinFET」とも呼ばれる3次元構造のトランジスタを採用している点で独自性がある。この3次元トランジスタによって、最先端のチップにおける最大の課題ともいえる、リーク電流に起因した消費電力を低減できると期待されている。他のチップメーカーは、同様の技術を20nm以降のプロセス世代で導入していくとしている。

UBM TechInsightsは今後、このIvy Bridgeを走査透過電子顕微鏡(STEM:Scanning and Transmission Electron Microscopy)や広がり抵抗測定(SRP:Spreading Resistance Profiling)、X線技術を使ってさらに詳しく解析し、結果を2本のリポートにまとめて発行する予定だ。

1本目は5月上旬に用意できる見込みで、プロセス技術や、内蔵メモリ、ロジックセル、I/O用トランジスタを取り上げ、チップの高解像度の画像も提供する。2本目は5月半ばに発行する予定で、トランジスタの特性について詳しく分析するという。このチップに使われているn型/p型MOSトランジスタの電気的なDC特性の他、ゲートリーク電流およびチャネルリーク電流のデータや、3つの異なる温度で測定した性能ベンチマークの結果も記載する。

- Samsung「Galaxy S7 Edge」を分解

- 第6世代iPod touchを分解、目を引く「A8」

- 「LG G4」を分解、量子ドットディスプレイを採用

- Apple WatchをX線写真で見るとこうなる! 「S1」の搭載部品も

- Apple WatchのBOMは販売価格の1/4、多大な利益を得られる可能性も

- Apple Watchを分解、心臓部の「S1」がお目見え

- Samsung 14nmプロセッサ「Exynos」に刻まれた文字から探る

- Samsung「Galaxy S6 edge」を分解

- 「HTC One M9」を分解

- 「MacBook Air(Early 2015)」13インチモデルを分解

- 「Nexus 9」を分解

- Newニンテンドー3DS LLを分解

- どこまで同じ? iPad mini 2とiPad mini 3

- 「Nexus 6」を分解

- 「世界初」のワイヤレス音楽キーボード「C.24」を分解

- 「iPad Air 2」を分解

- 「iPhone 6」を分解

- 「iPhone 6 Plus」を分解

- 小型無人航空機(ドローン)のパイオニア、「AR.Drone 2.0」を分解

- Amazonの「Fire Phone」を分解、iPhone並みの高性能チップを搭載

- Samsungの新スマートウオッチ「Gear 2」を分解

- 「GALAXY S5」を分解、心拍から指紋までセンサーの存在感が際立つ

- 「Xbox One」を分解

- 「プレステ4」を分解

- iPad Airの「A7」は、iPhone 5sよりも高速!?

- GALAXY Note 3を分解、3GビットのLPDDR3を搭載

- iPhone 5s メインボードの搭載チップは?

- iPhone 5s搭載「M7コプロセッサ」はNXP製マイコン――Chipworksが分解

- 「iPhone 5S」を解剖!? 気になる新機能と搭載部品を探る

- Google Glassを分解

- Xbox 360の最終形は、ある意味“初代Xbox One”だった

- 第5世代iPod touch 16GB版を分解

- HTCの最新スマホ「HTC One」を分解、筐体が開けにくく修理は“非常に困難”

- Samsungの「GALAXY S4」を分解、本丸はCortex-A7/A15の8コアプロセッサ

- ダイソンの新掃除機、4年かけて開発したモーターで40%静かに

- BlackBerryの最新スマホを分解、「GALAXY S III」の採用品を数多く搭載

- 新型iPad用プロセッサ「A6X」の詳細が判明、4コアGPUで性能を増強

- Appleの「iPad mini」を分解、A5プロセッサは32nmのHKMG技術で製造

- Amazonの「Kindle Fire HD」を分解、Apple・Google対抗の小型タブレット

- iPhone 5を分解、新型プロセッサ「A6」の謎に迫る

- 電気自動車「ボルト」、電池管理の秘密

- 小型iPad投入あおるGoogleの「Nexus 7」、部品ベンダーに見慣れぬ顔ぶれ

- Samsungの最新スマホ「GALAXY S III」を分解、クアッドコアのダイ写真も公開

- 電気自動車「シボレー・ボルト」を解剖、電力システムの秘密に迫る

- Intelの新型CPU「Ivy Bridge」を早速解剖、3DトランジスタのTEM画像公開

- まずはヒートガンでシーリング材を軟化、新型iPadの分解手順をリポート

- 第3世代iPadを分解、新型プロセッサ「A5X」と従来品の差異が明らかに

- Samsungの「Galaxy Nexus i515」を分解、LTEチップの価格が旧品種の半分に

- 「これじゃユーザーが開けられない」、AppleのネジをiFixitのCEOが批判

- 太陽のエネルギーが電力網につながるまで、PVインバータ「Sunny Boy」に学ぶ

関連キーワード

Ivy Bridge | Intel | トランジスタ | 3D | 22nmプロセス | Sandy Bridge | CPU | 半導体 | 28nmプロセス | Core iシリーズ | プロセス技術(エレクトロニクス) | Core i7 | アルテラ | Core i5 | 製品解剖 | GLOBALFOUNDRIES | ムーアの法則 | QUALCOMM(クアルコム) | SRAM | TSMC | ザイリンクス

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

Ivy Bridgeの断面画像 透過型電子顕微鏡(TEM)による断面画像である。3次元構造のトランジスタ素子が確認できる。出典:UBM TechInsights

Ivy Bridgeの断面画像 透過型電子顕微鏡(TEM)による断面画像である。3次元構造のトランジスタ素子が確認できる。出典:UBM TechInsights Ivy Bridgeのダイ写真 ダイサイズは170mm2である。出典:UBM TechInsights

Ivy Bridgeのダイ写真 ダイサイズは170mm2である。出典:UBM TechInsights Sandy Bridgeのダイ写真 Sandy Bridgeの「Core i7 2600K」である。ダイサイズは208mm2と比較的大きい。出典:UBM TechInsights

Sandy Bridgeのダイ写真 Sandy Bridgeの「Core i7 2600K」である。ダイサイズは208mm2と比較的大きい。出典:UBM TechInsights